## Critical Reviews in Solid State and Materials Sciences

Publication details, including instructions for authors and subscription information:

<http://www.tandfonline.com/loi/bsms20>

### Electrical Modeling of Thin-Film Transistors

D. Hong <sup>a</sup> , G. Yerubandi <sup>a</sup> , H. Q. Chiang <sup>a</sup> , M. C. Spiegelberg <sup>a</sup> & J. F. Wager <sup>a</sup>

<sup>a</sup> School of Electrical Engineering and Computer Science , Oregon State University , Corvallis, Oregon, 97331-5501, USA

Published online: 19 May 2008.

To cite this article: D. Hong , G. Yerubandi , H. Q. Chiang , M. C. Spiegelberg & J. F. Wager (2008) Electrical Modeling of Thin-Film Transistors, Critical Reviews in Solid State and Materials Sciences, 33:2, 101-132, DOI: [10.1080/10408430701384808](https://doi.org/10.1080/10408430701384808)

To link to this article: <http://dx.doi.org/10.1080/10408430701384808>

PLEASE SCROLL DOWN FOR ARTICLE

Taylor & Francis makes every effort to ensure the accuracy of all the information (the "Content") contained in the publications on our platform. However, Taylor & Francis, our agents, and our licensors make no representations or warranties whatsoever as to the accuracy, completeness, or suitability for any purpose of the Content. Any opinions and views expressed in this publication are the opinions and views of the authors, and are not the views of or endorsed by Taylor & Francis. The accuracy of the Content should not be relied upon and should be independently verified with primary sources of information. Taylor and Francis shall not be liable for any losses, actions, claims, proceedings, demands, costs, expenses, damages, and other liabilities whatsoever or howsoever caused arising directly or indirectly in connection with, in relation to or arising out of the use of the Content.

This article may be used for research, teaching, and private study purposes. Any substantial or systematic reproduction, redistribution, reselling, loan, sub-licensing, systematic supply, or distribution in any form to anyone is expressly forbidden. Terms & Conditions of access and use can be found at <http://www.tandfonline.com/page/terms-and-conditions>

# Electrical Modeling of Thin-Film Transistors

**D. Hong, G. Yerubandi, H. Q. Chiang, M. C. Spiegelberg, and J. F. Wager\***

*School of Electrical Engineering and Computer Science, Oregon State University, Corvallis, Oregon 97331-5501, USA*

An overview of device physics-oriented electrical modeling of thin-film transistors (TFTs) is presented. Four specific models are considered: (i) square-law, (ii) 3-layer, (iii) comprehensive depletion-mode, and (iv) discrete trap. For each model, a functional assessment of model equations is undertaken in terms of independent and dependent variables, model parameters, physical operating parameters, and constraining inequalities in order to facilitate mapping of model equations into a corresponding equivalent circuit. Channel mobility and “subthreshold” current trends are elucidated. Finally, a conductance integral equation based on Shockley’s gradual channel approximation is introduced and is employed in model development and device assessment.

**Keywords** thin-film transistor, device modeling, square-law model, 3-layer model, comprehensive depletion-mode model, discrete trap model, conductance integral equation, channel mobility, fringing current artifacts, series resistance, trapping

## Table of Contents

|                                                                                                         |     |

|---------------------------------------------------------------------------------------------------------|-----|

| <b>I. INTRODUCTION</b> .....                                                                            | 102 |

| <b>II. BACKGROUND</b> .....                                                                             | 103 |

| A. Device Structure and Operation .....                                                                 | 103 |

| B. Ideal Square-Law Model Overview .....                                                                | 104 |

| C. Model Non-Idealities .....                                                                           | 105 |

| <b>III. SQUARE-LAW MODEL</b> .....                                                                      | 106 |

| A. Model Derivation .....                                                                               | 106 |

| B. Simulation Results .....                                                                             | 107 |

| C. Series Resistance Effects .....                                                                      | 107 |

| <b>IV. CONDUCTIVE CHANNEL MODELS</b> .....                                                              | 109 |

| A. 3-Layer Model Overview .....                                                                         | 109 |

| B. Application of the 3-Layer Model Applied to SnO <sub>2</sub> Transparent Thin-Film Transistors ..... | 110 |

| C. Comprehensive Depletion-Mode Model .....                                                             | 111 |

| <b>V. DISCRETE TRAP MODEL</b> .....                                                                     | 115 |

| A. Model Overview .....                                                                                 | 115 |

| B. Simulation Results: Subthreshold Current Considerations .....                                        | 116 |

| C. Simulation Results: Above-Threshold Effects of Trap Density and Energy Depth .....                   | 119 |

| <b>VI. MOBILITY</b> .....                                                                               | 119 |

| A. Effective and Field-Effect Mobilities .....                                                          | 119 |

| B. Average and Incremental Mobilities .....                                                             | 120 |

\*E-mail: jfw@eecs.oregonstate.edu

|                                                                 |            |

|-----------------------------------------------------------------|------------|

| C. Simulation Results: Ideal Mobility Extraction .....          | 121        |

| D. Apparent Mobility Degradation due to Series Resistance ..... | 121        |

| E. Mobility Degradation due to a Discrete Trap .....            | 122        |

| F. Unpatterned Channel, Fringing Current Artifacts .....        | 123        |

| <b>VII. CONCLUSIONS .....</b>                                   | <b>125</b> |

| <b>ACKNOWLEDGMENTS .....</b>                                    | <b>125</b> |

| <b>REFERENCES .....</b>                                         | <b>125</b> |

| <b>X. APPENDICES .....</b>                                      | <b>126</b> |

| A. Square-Law Model with Series Resistance .....                | 126        |

| B. Conductance Integral Equation Modeling .....                 | 126        |

| 1. Conductance Integral Equation .....                          | 126        |

| 2. Enhancement-Mode Current Model .....                         | 127        |

| 3. Comprehensive Depletion-Mode Current Model .....             | 128        |

| a. Depletion-mode conductance .....                             | 128        |

| b. Depletion-mode current voltage characteristics. ....         | 129        |

| C. Discrete Trap Model Derivation .....                         | 131        |

## I. INTRODUCTION

Literature devoted to device physics assessment of thin-film transistor (TFT) operation can be categorized into three eras, the 1960s,<sup>1–3</sup> the 1980s,<sup>4–6</sup> or relatively recent.<sup>7–12</sup> These diverse dates reflect, respectively, the birth of TFTs, the realization of amorphous silicon TFTs for display applications, and the development of polycrystalline silicon TFTs for display and other applications, as well as a resurgent interest in TFTs for emerging applications involving large-area, low-cost, printed, flexible, and/or transparent electronics.

There are several possible reasons for undertaking electrical device modeling. Probably the most common device modeling objective is to develop circuit-oriented SPICE models in order to facilitate computer-aided design of circuits and electronic systems. Other objectives include understanding the physical nature of device operation and device optimization. Several excellent references dedicated to modeling have recently been published.<sup>11–12</sup> These references focus specifically on amorphous and polycrystalline silicon TFT modeling, concentrating on materials topics pertinent to such devices including band-tail and localized gap states, dispersive transport, threshold voltage metastability, diffusion current, as well as grain boundary trapping, passivation, and transport. The present article does not concern these topics as they are more pertinent to fully developed material systems and, in some cases, for example, diffusion current, are not applicable to the wide-bandgap materials of primary interest to this article.

Rather, the objective of this review article is to present an overview of generic device modeling of electrical properties of a TFT from the perspective of the development of new materials and emerging applications. Our motivation for pursuit of this topic stems from our recent research efforts in the development

of transparent electronics. It is our experience that the type of modeling presented herein is useful for the elucidation of non-ideal device characteristics, which are often encountered in the development of new TFT materials and device structures.<sup>13–18</sup> Thus, it is our hope that the models discussed herein will find use in the advancement of organic, oxide-based, or other types of emerging or future TFT technologies.

This article is not a “review article” in the conventional sense because much of what is included has never before been published. Moreover, even when classical topics are addressed, we have attempted to present them from a unique perspective.

The topics included in this article are as follows. Background information, including basic device structure and operation, an overview of the ideal square-law model, and typical non-idealities encountered in wide band gap TFTs are discussed in section II. A more complete discussion of the ideal square-law model, including series resistance effects, is given in section III. Section IV models the effects of a conductive channel. Section V is devoted to a discrete trap model, which is useful for elucidating many types of TFT device electrical characteristic trends, because traps almost always play a fundamental role in TFT operation. Additionally, the effects of the discrete trap in establishing both subthreshold and above-threshold regimes of operation are discussed. Channel mobility is considered in section VI. Two types of mobility, average and incremental mobility, are proposed as preferable replacements for the more venerable effective and field-effect mobilities typically utilized in field-effect transistor (FET) assessment. Simulations employing the discrete trap model demonstrate the importance of trapping in establishing mobility trends. Finally, the Appendix provides a derivation of the ideal square-law model equations and discusses the effects of series resistance, which do not significantly affect

the prototypical staggered bottom-gate, wide band gap TFTs, but may be useful for TFTs based on other channel materials and structures. Additionally, the conductance integral equation is introduced and is applied to derive current-voltage equations for both an enhancement-mode and a depletion-mode TFT. Finally, the discrete trap model equations are also derived in the Appendix.

## II. BACKGROUND

The primary objective of this section is to provide a general background of thin-film transistors. First, several TFT device structures and fundamental device operation are discussed. Second, quantitative analysis of an ideal TFT is provided. Finally, several non-idealities observed in the development of wide band gap channel materials are discussed. However, note that non-idealities specific to circuit design or implementation, such as parasitic resistances, parasitic capacitances, and short-channel effects are not considered.

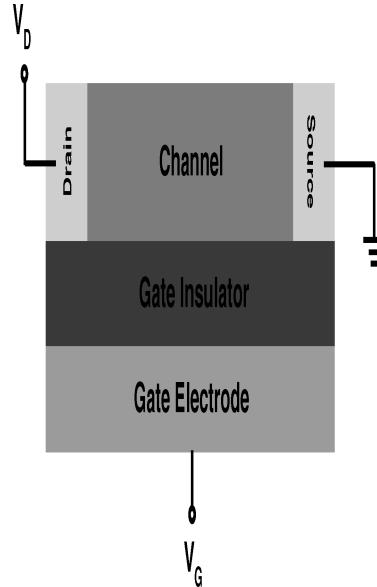

### A. Device Structure and Operation

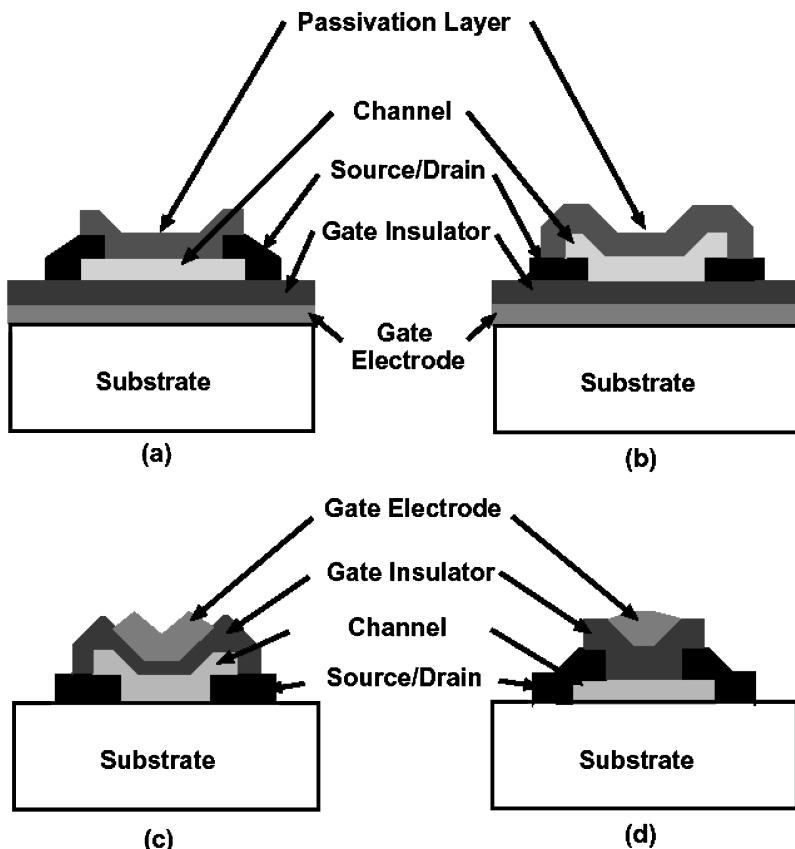

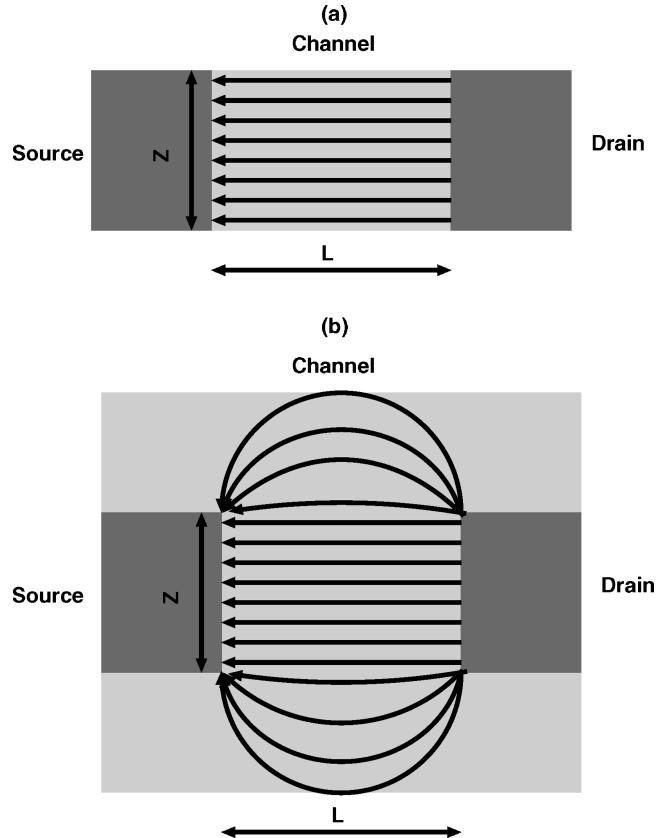

Four possible TFT device structures are shown in Figure 2.1.<sup>10</sup> Devices can be either staggered or coplanar. In a coplanar configuration, as shown in Figures 2.1(b) and 2.1(d),

the source/drain contacts and the insulator are on the same side of the channel. In such an arrangement, the source/drain contacts are in direct contact with the induced channel such that current flows in a single plane. In a staggered configuration, as shown in Figures 2.1(a) and 2.1(c), the source/drain contacts are on the opposite side of the channel from the insulator. Thus, there is no direct connection to the induced channel. Current must flow vertically to the induced channel before flowing horizontally toward the drain. However, the contact area is very large when a staggered structure is used, resulting in minimal contact resistance.

In addition to coplanar and staggered configurations, TFTs can be classified as either bottom-gate or top-gate devices. In a bottom-gate TFT, which is sometimes referred to as an inverted TFT, the gate insulator and gate electrode are located beneath the channel, as shown in Figures 2.1(a) and 2.1(b). The top surface of a bottom-gate TFT is exposed to air or passivated by coating the top surface with a protective layer. A top-gate TFT, as shown in Figures 2.1(c) and 2.1(d), has the gate and insulator located on top of the channel. In a top-gate device, the channel is covered by a gate insulator so that the top surface is inherently passivated.

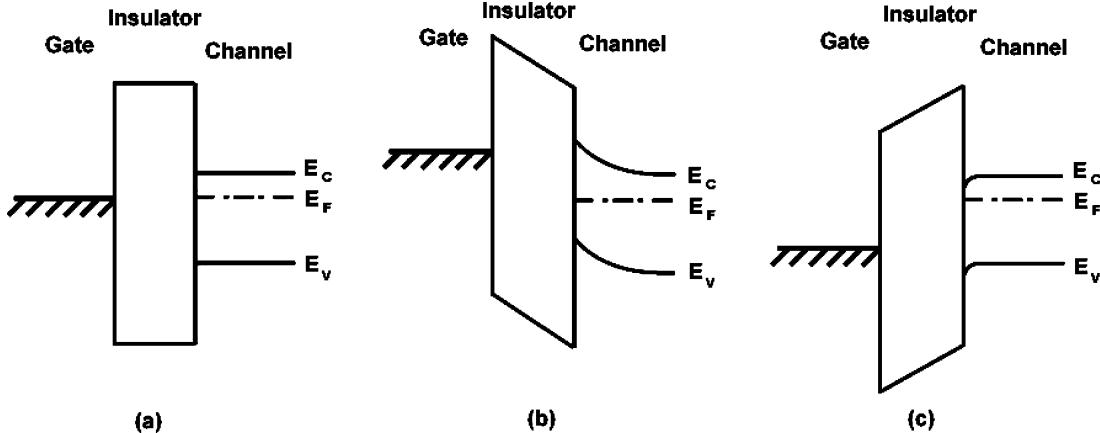

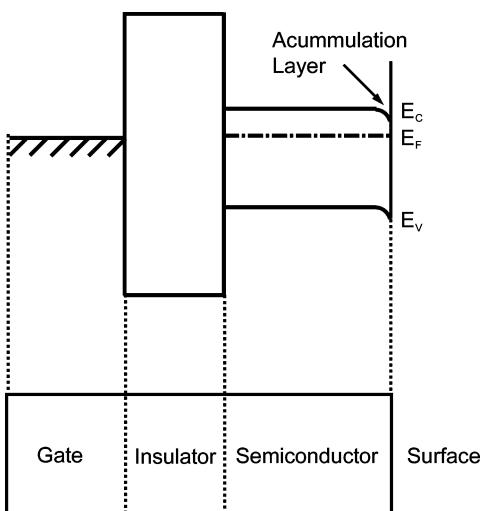

Figure 2.2 shows several ideal energy band diagrams (neglecting any passivation layer) as viewed through the gate of

FIG. 2.1. Four general thin-film transistor configurations, including: (a) staggered bottom-gate, (b) coplanar bottom-gate, (c) staggered top-gate, and (d) coplanar top-gate.

FIG. 2.2. Energy band diagrams as viewed through the gate for several biasing conditions: (a) equilibrium, (b) depletion ( $V_{GS} < 0$  V), and (c) accumulation ( $V_{GS} > 0$  V).

an n-channel, accumulation-mode TFT.<sup>3</sup> The energy band diagram of Figure 2.2(a) shows the device at equilibrium, that is, 0 V applied to the source, drain, and gate. Figure 2.2(b) shows an energy band diagram with the gate negatively biased. The applied negative bias repels mobile electrons from the channel, leaving a depletion region near the channel/insulator interface. When compared to Figure 2.2(a), this biasing condition has reduced conductance due to a reduced number of mobile electrons in the channel. Figure 2.2(c) shows an energy band diagram with the gate positively biased. The applied positive bias attracts mobile electrons, forming an accumulation region near the insulator–channel interface. These excess mobile electrons lead to an increase in the conductance.

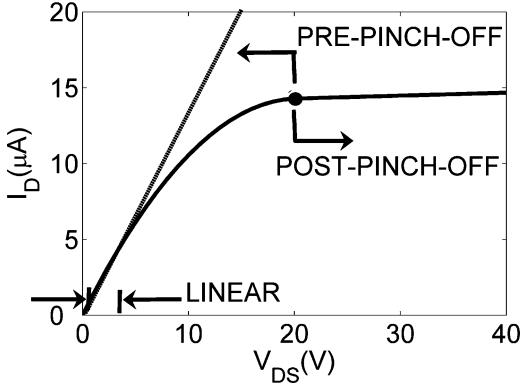

Beginning with the case shown in Figure 2.2(c), consider the effect of an applied drain to source voltage,  $V_{DS}$ . As  $V_{DS}$  is increased from 0 V, the channel is initially modeled as a resistor, that is, current increases linearly with increasing  $V_{DS}$ . However, as  $V_{DS}$  increases, accumulation near the drain decreases. As  $V_{DS}$  is increased further, the region near the drain eventually begins to deplete. The voltage at which the channel region near the drain is fully depleted of electrons, or pinched off, is denoted the saturation voltage,  $V_{DSAT}$ . Therefore, application of  $V_{DS} \geq V_{DSAT}$  results in a saturated drain current characteristic.

A distinguishing feature of a TFT compared to a conventional metal-oxide-semiconductor field-effect transistor (MOSFET) is that carrier transport in the channel typically occurs in an *accumulation* layer in a TFT and in an *inversion* layer in a MOSFET. A TFT, just like a MOSFET, can operate as either an *enhancement-mode* or a *depletion-mode* device. Enhancement-mode devices are *normally off*, that is, negligible drain current flows at zero gate bias. Such normally off devices dissipate less power when in a standby mode, and also more readily facilitate the accomplishment of digital logic and analog circuit functions. This is in contrast to depletion-mode devices, which are *normally on* devices; such devices are useful for certain elec-

tronic applications, for example, active-load for a logic inverter, but, in general, are not as valuable electronic components for designing circuits and systems.

### B. Ideal Square-Law Model Overview

As discussed in the previous subsection, the current that flows in a TFT is dependent on two applied voltages,  $V_{GS}$  and  $V_{DS}$ . For an ideal transistor, the drain current is described by the square-law model equations.<sup>2,19</sup> For drain voltages less than  $V_{DSAT}$ , the ideal square-law model states that

$$I_D = \frac{Z\mu C_G}{L} \left[ (V_{GS} - V_{ON})V_{DS} - \frac{V_{DS}^2}{2} \right], \quad (V_{DS} < V_{DSAT}) \quad [2.1]$$

where  $I_D$  is the drain current,  $Z$  is the channel width,  $L$  is the channel length,  $\mu$  is the mobility,  $V_{ON}$  is the turn-on voltage, and  $C_G$  is the gate capacitance per unit area. When  $V_{DS}$  greater than  $V_{GS} - V_{ON}$  is applied, the channel is pinched off and the drain current is saturates at

$$I_{DSAT} = \frac{Z\mu C_G}{2L} (V_{GS} - V_{ON})^2 . (V_{DS} \geq V_{DSAT}) \quad [2.2]$$

A complete derivation of the ideal-square law model is presented in section III.A, and also in section X.B in the context of the conductance integral equation.

Equations 2.1–2.2 are the central equations constituting the square-law model. The “square-law” designation arises from the quadratic dependence displayed in Eq. 2.2 in which the saturation current is proportional to the square of the applied gate voltage in excess of the turn-on voltage. Those familiar with the ideal square-law may notice that the threshold voltage,  $V_T$ , has been replaced by  $V_{ON}$  in Eqs. 2.1 and 2.2. In this article,  $V_T$  and  $V_{ON}$  are utilized as follows.  $V_T$  is the extrapolated value from the linear portion of a pre-pinch-off  $I_D - V_{GS}$  curve, thus giving the voltage at which appreciable current flows.  $V_{ON}$  quantifies the onset of drain current conduction through the use of

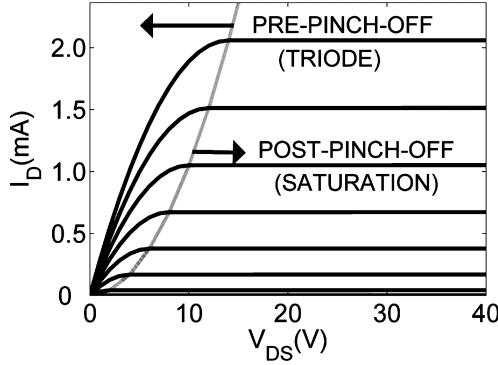

FIG. 2.3. Simulated drain current-drain voltage ( $I_D - V_{DS}$ ) characteristics for an n-channel, depletion-mode TFT modeled using the ideal square-law model. The dashed curve identifies a locus of  $V_{DSAT}$ 's. The top curve corresponds to a gate voltage of 9 V, with the gate voltage decremented by 2 V for each subsequent curve. Square-law model parameters employed for this simulation are:  $V_{ON} = -5$  V,  $C_G = 70$  nF/cm<sup>2</sup>,  $\mu = 30$  cm<sup>2</sup>/V-s, and  $Z/L = 10:1$ .

the  $\log(I_D) - V_{GS}$  characteristic. A more detailed discussion of these quantities is provided in section V.B.

Several assumptions are made in the derivation of the square-law model. The primary assumption is the gradual channel approximation. The gradual channel approximation assumes that in the channel, the electric field perpendicular to the channel is much greater than the electric field parallel to the channel. This assumption allows the two electric fields to be considered separately. The second major assumption is that charge in the channel varies linearly with respect to applied gate bias. Finally, it is assumed that all induced charge is due to free carriers, which have a uniform mobility.

The most fundamental attribute of a TFT is its set of  $I_D - V_{DS}$  characteristics. Figure 2.3 illustrates  $I_D - V_{DS}$  behavior for varying values of  $V_{GS}$  simulated using the ideal square-law model. Several aspects of these characteristics merit consideration.

First, this TFT operates in depletion-mode, as evident from the fact that an appreciable current flows (sixth curve from the top) even when no gate voltage is applied. Enhancement-mode operation, in which negligible current flows until a sufficiently large positive voltage is applied to the gate (i.e.,  $V_{ON} > 0$  V), is preferable to depletion-mode behavior because circuit design is easier and power dissipation is minimized when normally off, enhancement-mode devices are employed.

Second, each  $I_D - V_{DS}$  curve is comprised of a pre-pinchoff or triode regime, described by Eq. 2.1, and a post-pinchoff or saturation regime at which the current is constant with respect to  $V_{DS}$  and is given by Eq. 2.2. These two operating regimes intersect at  $V_{DS} = V_{DSAT} = V_{GS} - V_{ON}$ , which corresponds to the minimum drain voltage at which the entire channel thickness near the drain is depleted of free carriers.

Third, the ideal device shown in Figure 2.3 exhibits “hard saturation,” as witnessed by the fact that the slope of each  $I_D$

curve is zero in the post-pinchoff or saturation regime. Hard saturation indicates that the entire thickness of the channel is depleted of free carriers. Hard saturation is desirable for most circuit applications, because a transistor exhibiting this property possesses large output impedance.

A fourth and final aspect of Figure 2.2 that warrants comment involves the magnitude of the current. A large  $I_D$  is always desirable. An assessment of Eq. 2.2 indicates that there are three primary ways to increase  $I_D$ . First, modifying the TFT geometry by increasing the magnitude of  $Z/L$  increases  $I_D$ . Second, increasing the gate dielectric constant, and hence the gate capacitance,  $C_G$ , results in more current. Finally, a higher mobility yields higher current.

### C. Model Non-Idealities

Several non-idealities must be considered in order to accurately model the current-voltage characteristics of a wide band gap TFT.

First, it is possible that series resistance at the source and/or the drain can lead to a decrease in the drain current and to a concomitant apparent decrease in the channel mobility. In practice, we usually find series resistance to be of negligible importance in determining the operation of a wide band gap TFT. However, for completeness, series resistance effects related to the drain current and to the mobility are considered in sections III.C and VI.D, respectively.

Second, if a high “bulk” carrier concentration is present in the channel of a TFT, the induced charge density does not vary linearly with respect to the applied gate voltage, as assumed in the ideal square-law model. This conductive channel case is treated in section IV in terms of the 3-layer model and, more accurately, the comprehensive depletion-mode model. The comprehensive depletion-mode model is developed in the context of the conductance integral equation, as described in section X.B.

Third, traps play a critical role in determining TFT operation. Trapping of carriers injected into the channel is responsible for many subthreshold and above-threshold trends, as presented in sections V.B and V.C, respectively, in the context of the discrete trap model, as previously introduced by Sze.<sup>3</sup> Additionally, carrier trapping leads to mobility degradation, as discussed in section VI.E.

Fourth, many TFT current-voltage non-idealities involve the channel mobility. We contend that the use of average and incremental mobility instead of effective and field-effect mobility results in less ambiguity when trying to understand channel mobility trends. These and other mobility issues are discussed in section VI. As already mentioned, series resistance or trapping degrade the apparent or actual channel mobility, respectively, as described in sections VI.D and VI.E. Additionally, an unpatterned channel layer results in fringing current flowing around the channel edges of a TFT. This leads to possible overestimation of the channel mobility, as considered in section VI.F. Finally, surface roughness scattering can affect the mobility of carriers in the large applied gate bias regime. This effect, although not

directly considered in this article, can easily be taken into account, either as a model refinement or using empirical data, via the conductance integral equation introduced in section X.B. Moreover, the conductance integral equation can be used to develop new model equations that account for any arbitrary conductance effect.

### III. SQUARE-LAW MODEL

#### A. Model Derivation

In 1963, Borkan and Weimer<sup>20</sup> published their analysis of TFT device behavior based on Shockley's gradual channel approximation analysis of the junction field-effect transistor. The essence of this gradual channel approximation is as follows. Field-effect transistors inherently pose a two-dimensional electric field problem, involving electric field components both parallel and perpendicular to the flow of current in the channel. Shockley's gradual channel approximation invokes the assumption that the lateral change in the electric field along the channel (y-component) is much less than the change in the electric field perpendicular to the channel (x-component).<sup>21</sup> By making this assumption, the two-dimensional electric field problem simplifies into two separate one-dimensional problems involving gate voltage modulation of carriers in the channel and drain voltage-induced transport of carriers along the channel. It is important to note that the gradual channel approximation is only valid for long-channel devices, where the lateral electrical field can be neglected, and for device operation in the pre-pinch-off regime, as defined in the following discussion.

We begin the development of the ideal square-law model by treating the TFT gate, insulator, and semiconductor channel as an ideal metal-oxide-semiconductor (MOS) capacitor and employing the relationship  $Q = C \times V$  to determine the total induced charge. Substituting in appropriate terms, we obtain,

$$q \Delta n(y) = \frac{C_G}{h} [V_{GS} - V(y)], \quad [3.1]$$

where  $q \Delta n(y)$  is the gate-induced charge density,  $C_G$  is the gate capacitance per unit area,  $V_{GS}$  is the gate voltage,  $h$  is the thickness of the semiconductor channel, and  $V(y)$  is the channel voltage obtained at a distance "y" along the channel.

Assuming that mobility,  $\mu$ , is constant along the channel and that the channel current is dominated by drift, the drain current,  $I_D$ , is given by,

$$I_D = hZ [\sigma_o + \sigma(y)] \xi(y), \quad [3.2]$$

where  $Z$  is the channel width,  $\xi(y)$  is the electric field along the channel,  $\sigma_o$  is the channel conductivity at zero gate bias, and  $\sigma(y)$  is the channel conductivity due to the induced charge density. The drain current may be rewritten by noting that  $\sigma = q\mu n$ , resulting in,

$$I_D = hZq\mu [n_o + \Delta n(y)] \xi(y), \quad [3.3]$$

where  $n_o$  is the initial carrier density in the semiconductor and  $\Delta n(y)$  is the gate-induced carrier density. Substituting Eq. 3.1 into Eq. 3.3 and expressing the electric field in terms of the voltage drop along the channel yields,

$$I_D = Z\mu C_G \left[ \frac{qhn_o}{C_G} + V_{GS} - V(y) \right] \frac{dV(y)}{dy}. \quad [3.4]$$

Operating on both sides of Eq. 3.4 by  $dy$  and then integrating over the length of the channel,  $L$ , we obtain,

$$I_D \int_0^L dy = Z\mu C_G \int_0^{V_{DS}} \left[ \frac{qhn_o}{C_G} + V_{GS} - V(y) \right] dV(y). \quad [3.5]$$

Performing the integrations specified in Eq. 3.5 and dividing by  $L$  yields,

$$I_D = \frac{Z\mu C_G}{L} \left[ (V_{GS} - V_{ON})V_{DS} - \frac{V_{DS}^2}{2} \right], \quad [3.6]$$

where the turn-on voltage,  $V_{ON}$ , is given by,

$$V_{ON} = \frac{-qhn_o}{C_G}. \quad [3.7]$$

It is important to note that Eq. 3.6 is only valid when  $V_{GS} \geq V_{ON}$  and when the drain voltage is less than that required to pinch-off the channel, that is, when  $V_{DS} \leq V_{GS} - V_{ON}$ . Equation 3.6 is not applicable in either cut-off, that is, when  $V_{GS} < V_{ON}$  or in saturation, that is, when  $V_{DS} \geq V_{GS} - V_{ON}$ . Saturation is specified to occur when the channel is pinched off, given by the condition  $V_{DS} = V_{DSAT} = V_{GS} - V_{ON}$ , which when substituted into Eq. 3.6 yields,

$$I_{DSAT} = \frac{ZC_G\mu}{2L} (V_{GS} - V_{ON})^2. \quad [3.8]$$

Equations 3.6–3.8 are the central equations constituting the square-law model. The "square-law" designation arises from the quadratic dependence displayed in Eq. 3.8 in which the saturation current is proportional to the square of the applied gate voltage in excess of the turn-on voltage.

A complete description of the square-law model is given in Table 3.1. Three regimes of TFT operation are indicated: cut-off, pre-pinch-off (typically denoted "triode"), and post-pinch-off (typically denoted "saturation"). The corresponding constraint relations correspond to the gate voltage with respect to  $V_{ON}$  and the drain voltage with respect to  $V_{DSAT}$ .

An important function of a device physics-based model, such as the square-law model specified in Table 3.1, is associated with its utility for circuit simulation. Development of a circuit simulation model requires mapping of device physics equations into an appropriate equivalent circuit. To accomplish this mapping in a systematic manner, it is useful to identify the independent and dependent model variables (IV, DV), model parameters (MP), and physical operating parameters (POP) and to then specify them in the following functional form,

$$DV(IV_1, IV_2, \dots; MP_1, MP_2, \dots; POP_1, POP_2), \quad [3.9]$$

TABLE 3.1

Summary of the square-law model

| Variable designation | Equation                                                                  |

|----------------------|---------------------------------------------------------------------------|

| Turn-on voltage      | $V_{ON} = \frac{-qhn_0}{C_G}$                                             |

| Pinch-off condition  | $V_{DSAT} = V_{GS} - V_{ON}$                                              |

| Regime of operation  | Equation                                                                  |

| Cut-off              | $I_D = 0$                                                                 |

| Pre-pinchoff         | $I_D = \frac{Z\mu C_G}{L} [(V_{GS} - V_{ON})V_{DS} - \frac{V_{DS}^2}{2}]$ |

| Post-pinchoff        | $I_{DSAT} = \frac{Z\mu C_G}{2L} (V_{GS} - V_{ON})^2$                      |

| Model parameters     | Geometrical-based<br>Channel-based                                        |

|                      | $Z, L, h, C_G$<br>$n_0, \mu$                                              |

Employing this procedure to square-law theory yields,

$$I_D(V_{GS}, V_{DS}; Z, L, n_0, h, C_G, \mu; \text{none}). \quad [3.10]$$

Expressing the square-law model in this functional form allows one to quickly discern the two independent variables, six model parameters, and zero explicit physical operating parameters. (It could be argued that  $n_0$  and  $\mu$  implicitly depend on temperature, at least in a real device, so that temperature should be considered to be an implicit physical operating parameter.)

Note that, in general, the number of model parameters is not unique because a model may be expressed in various forms. For example, a circuit engineer would typically combine,  $\mu$  and  $C_G$  into one model parameter, thus reducing the number of model parameters. Model parameter specification is usually driven by the objective of the modeler. In the context of this review article, our primary motive is to elucidate TFT device physics operation. Therefore, we typically avoid model parameter compression since it tends to obscure the operating physics. As indicated in Table 3.1, model parameters can also be sub-categorized based on whether they involve device geometry or properties of the materials comprising the device.

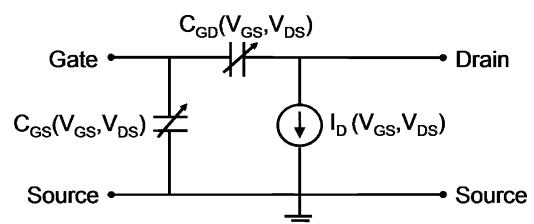

In order to map a device physics-based model into an appropriate equivalent circuit, identification of independent and dependent variables in a functional format is essential. Thus, establishing  $I_D(V_{GS}, V_{DS})$  in the square-law model facilitates identification of a nonlinear, *voltage-controlled current source* as an appropriate equivalent circuit element. Two voltages,  $V_{GS}$  and  $V_{DS}$  control  $I_D$ .  $I_D$  is, in general, nonlinear with respect to  $V_{GS}$  or  $V_{DS}$  as evident from Eqs. 3.6 and 3.8.

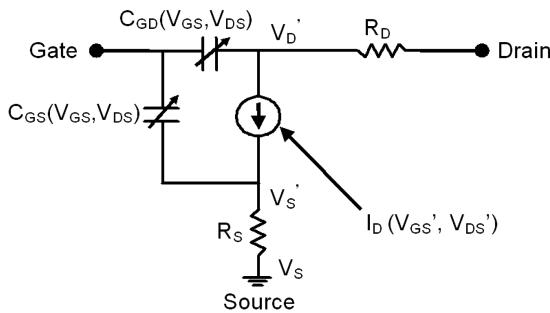

If a corresponding, but more complicated, device physics-based development is undertaken with respect to TFT capacitance-voltage (C-V) characteristics, it would require the incorporation of two additional nonlinear, voltage-controlled capacitors into the square-law, TFT equivalent circuit. Such an equivalent circuit is indicated in Figure 3.1. Because our primary modeling focus involves DC  $I_D - V_{DS}$  and  $I_D - V_{GS}$  assessment, we do not include C-V modeling in this review ex-

cept with respect to specification of equivalent circuits for the models discussed herein. However, it should be recognized that inclusion of these nonlinear, voltage-controlled capacitors are required for AC or transient modeling of TFTs.

### B. Simulation Results

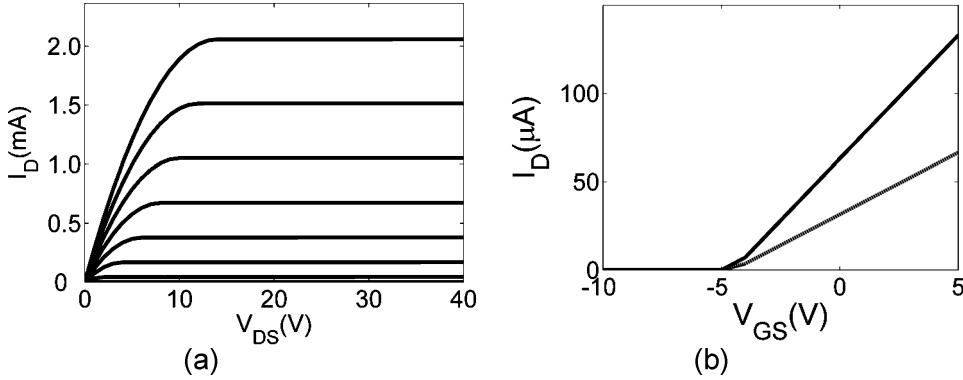

Figure 3.2 shows simulated  $I_D$  characteristics using the ideal square-law model. In Figure 3.2(a), the  $I_D - V_{DS}$  characteristic ( $V_{GS}$  is decreased from 9 to  $-3$  V in 2 V steps) is shown. This simulation results in  $\sim 2$  mA maximum current drive. In Figure 3.2(b),  $I_D - V_{GS}$  curves with  $V_{DS} = 1$  V, employing channel mobilities of 10 and  $30 \text{ cm}^2/\text{V}\cdot\text{s}$  are shown. Not only does the mobility affect the magnitude of the current at a given  $V_{GS}$  value, but it also changes the slope. Note that in the ideal case shown here, abrupt drain current turn-on at  $V_{ON}$  is observed. Moreover, for this ideal situation,  $V_T$  is equivalent to  $V_{ON} \sim -5$  V because the effect of carrier trapping, which is considered in section V, is neglected here.

### C. Series Resistance Effects

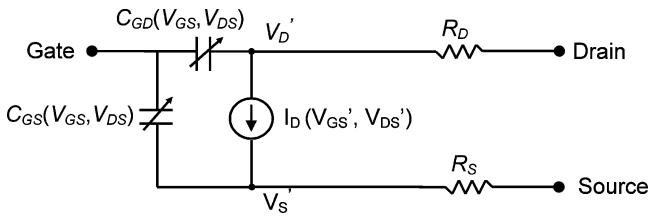

We begin our analysis of series resistance effects with the square-law model derived in the previous sub-section. Building on the square-law equivalent circuit model, resistors  $R_D$  and  $R_S$  are added at the source and the drain, as indicated in Figure 3.3.

FIG. 3.1. An equivalent circuit consisting of two nonlinear, voltage-controlled capacitors and a nonlinear, voltage-controlled current source corresponding to the square-law model specified by Table 3.1.

FIG. 3.2. Simulated (a)  $I_D - V_{DS}$  and (b)  $I_D - V_{GS}$  curve characteristics using the ideal square-law model. For the (a)  $I_D - V_{DS}$  characteristic,  $V_{GS}$  is decreased from 9 to  $-3$  V in 2 V steps. The (b)  $I_D - V_{GS}$  characteristics use  $V_{DS} = 1$  V and  $\mu = 10$  and  $30 \text{ cm}^2/\text{V-s}$  for the grey and black curves, respectively. Square-law model parameters employed for this simulation are:  $V_{ON} = -5$  V,  $C_G = 70 \text{ nF/cm}^2$ ,  $Z/L = 10:1$ , and  $\mu = 30 \text{ cm}^2/\text{V-s}$  (unless otherwise specified).

The addition of the series resistors results in  $I_D$  equations for the pre- and post-pinch-off regimes as follows. For the pre-pinch-off regime  $I_D$  is given by,

$$\begin{aligned} I_D &= \frac{ZC_G\mu}{L} \left( V'_{GS} - V_{ON} - \frac{V'_{DS}}{2} \right) V'_{DS} \\ &= \frac{ZC_G\mu}{L} \left( V_{GS} - I_D R_S - V_{ON} - \left( \frac{V_D - I_D(R_S + R_D)}{2} \right) \right) \\ &\quad \times (V_D - I_D(R_S + R_D)) \end{aligned} \quad [3.11]$$

where the primed quantities  $V_{GS}'$  and  $V_{DS}'$  represent internal voltages across the TFT from the gate-to-source and drain-to-source, respectively. The corresponding drain current equation for the post-pinch-off regime becomes,

$$\begin{aligned} I_D &= \frac{ZC_G\mu}{2L} (V'_{GS} - V_{ON})^2 \\ &= \frac{ZC_G\mu}{2L} (V_{GS} - I_D R_S - V_{ON})^2 \end{aligned} \quad [3.12]$$

The modified pinch-off condition is given by

$$V_{DSAT} = V_{GS} - V_{ON} + I_D R_D. \quad [3.13]$$

FIG. 3.3. Square-law model equivalent circuit for a TFT that includes the effects of source and drain series resistance. Primed quantities represent internal voltages.

A complete derivation of the series resistance equations, that is, Eqs. 3.11–3.13, is given in section IX.A.

A summary of the variables, equations, regimes of operation, constraints, and model parameters constituting the square-law model with the addition of series resistance is presented in Table 3.2.

It is evident from the model equations given that incorporation of  $R_S$  and  $R_D$  into the square-law model leads to a reduction in the drain current due to a concomitant decrease in effective terminal voltages. Additionally, comparing the pinch-off condition given in Eq. 3.13 reveals that  $V_{DSAT}$  has increased when compared to the ideal square-law model (excluding series resistance).

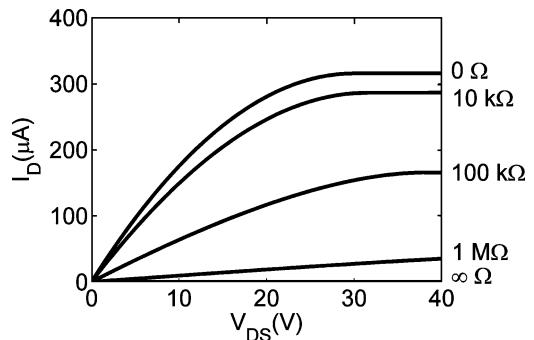

Figure 3.4 shows an example simulation which illustrates the effect of series resistance,  $R_{SERIES}$ , on an  $I_D - V_{DS}$  curve. In this simulation,  $R_{SERIES} = R_S + R_D$  and  $R_D = R_S$ . The two limits,  $R_{SERIES} = 0$  (top-curve) and  $R_{SERIES} = \infty\Omega$  (bottom-curve), are shown, as well as several intermediate values. At  $R_{SERIES} =$

FIG. 3.4. Simulated  $I_D - V_{DS}$  curves for varying values of series resistance. Parameters used for this simulation are:  $V_{GS} = 30$  V,  $R_{SERIES} = R_S + R_D$  and  $R_S = R_D$ .  $R_{SERIES} = [0 \Omega, 10 \text{ k}\Omega, 100 \text{ k}\Omega, 1 \text{ M}\Omega, \infty \Omega]$ .  $Z/L = 10$ ,  $h = 100 \text{ nm}$ ,  $C_G = 7 \times 10^{-7} \text{ F/cm}^2$ ,  $n_0 = 10^{14} \text{ cm}^{-3}$ , and  $\mu = 10 \text{ cm}^2/\text{V-s}$ .

TABLE 3.2

Summary of the square-law model with series resistance incorporated

| Variable definition | Equation                                                               |

|---------------------|------------------------------------------------------------------------|

| Turn-on voltage     | $V_{ON} = \frac{-qhn_0}{C_G}$                                          |

| Pinch-off condition | $V_{DSAT} = V_{GS} - V_{ON} + I_D R_D$                                 |

| Regime of operation | Equation                                                               |

| Cut-off             | $I_D = 0$                                                              |

| Pre-pinch-off       | $I_D = \frac{ZC_G\mu}{L}(V'_{GS} - V_{ON} - \frac{V'_{DS}}{2})V'_{DS}$ |

| Post-pinch-off      | $I_D = \frac{ZC_G\mu}{2L}(V'_{GS} - V_{ON})^2$                         |

| Model parameters    | Geometrical-based<br>Channel-based<br>Series resistance-based          |

|                     | $Z, L, h, C_G$<br>$n_0, \mu$<br>$R_S, R_D$                             |

0, the  $I_D - V_{DS}$  curve follows the ideal square-law model. As  $R_{SERIES}$  increases, an increasing fraction of the applied voltage is dropped across the parasitic series resistors, thereby internally biasing the TFT at a lower effective voltage, resulting in less current drive. Additionally, the voltage corresponding to pinch-off, which establishes the onset of saturation of an  $I_D - V_{DS}$  curve, increases with increasing series resistance (e.g.,  $V_{DSAT} = 30, 30.15, 31.4, 38.3, 49.5, 57$  V for  $R_{SERIES} = 0, 1$  k, 10 k, 100 k, 1 M, 10 M $\Omega$ , respectively). Thus,  $I_D$  does not saturate over the domain of  $V_{DS}$  shown in Figure 3.3 when  $R_{SERIES} > 1$  M $\Omega$ . The limiting case corresponds to all of the voltage being dropped across  $R_D$  and  $R_S$ , so that  $V'_{GS}$  and  $V'_{DS}$  are zero. Thus, the  $I_D - V_{DS}$  curve shows negligible current conduction when  $R_{SERIES} = \infty\Omega$ .

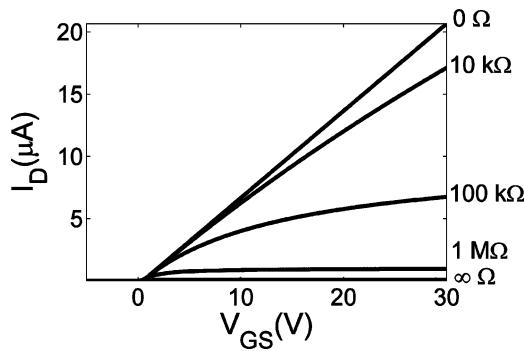

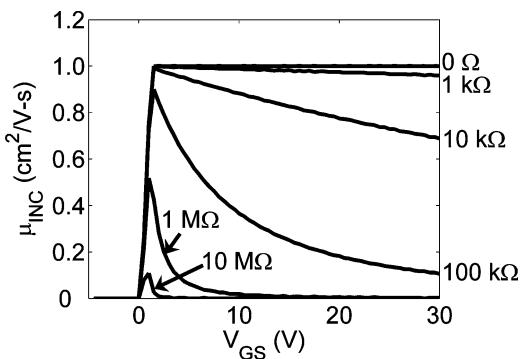

Figure 3.5 shows the effect of series resistance on an  $I_D - V_{GS}$  curve using the same values for  $R_{SERIES}$  as employed for Figure 3.5. It is evident from Figure 3.5 that the slope of the  $I_D - V_{GS}$  curve decreases with increasing series resistance. Note also that this slope increases nonlinearly with respect to  $V_{GS}$ .

FIG. 3.5. Simulated  $I_D - V_{GS}$  curves for varying values of series resistance.  $R_{SERIES} = R_S + R_D$  and  $R_D = R_S$ .  $V_{DS} = 1$  V.  $R_{SERIES} = [0 \Omega, 10 \text{k}\Omega, 100 \text{k}\Omega, 1 \text{M}\Omega, \infty\Omega]$ .  $Z/L = 10$ ,  $h = 100 \text{ nm}$ ,  $C_G = 7 \times 10^{-7} \text{ F/cm}^2$ ,  $n_0 = 10^{14} \text{ cm}^{-3}$ , and  $\mu = 10 \text{ cm}^2/\text{V}\cdot\text{s}$ .

This  $I_D - V_{GS}$  trend results in a severe degradation of the apparent mobility.

As mentioned previously, we typically find series resistance to be of negligible importance in determining the operation of wide band gap, inorganic oxide TFTs, however, the analysis provided here may be useful for elucidating the effects of reduced device dimensions.

#### IV. CONDUCTIVE CHANNEL MODELS

The ideal square-law model presented in section III provides an excellent framework for the development of more adaptable models. In this section, the 3-layer and comprehensive depletion-mode models are introduced to account for channels with an appreciably high carrier concentration. The 3-layer model provides an extremely simple means of modeling a conductive channel by adding two additional conduction paths, in parallel with the gate-induced channel current. Due to the simplicity of the 3-layer model, however, it has several deficiencies; these deficiencies are addressed in the comprehensive depletion-mode model.

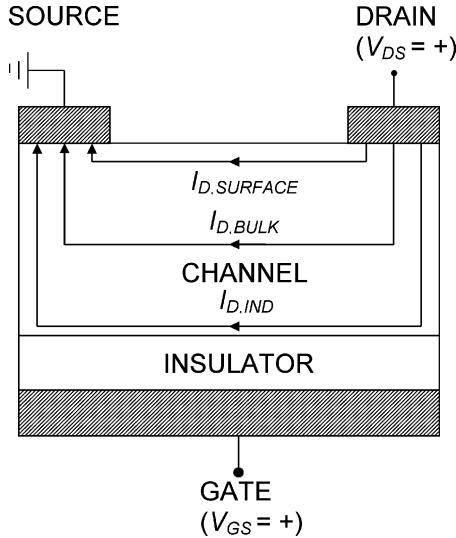

##### A. 3-Layer Model Overview

Figure 4.1 illustrates the 3-layer model. Two additional conduction paths are included in Figure 4.1 in addition to the “normal” drain current component,  $I_{D,IND}$ , which corresponds to the gate-induced current path developed in section III in the square-law model. The two additional conduction paths (bulk and surface) are modeled as resistors. Current flowing through the “bulk” portion of the channel,  $I_{D,BULK}$ , is associated with a uniform bulk resistance of the channel,

$$R_{BULK} = \frac{L}{q\mu N_D h Z} \quad [4.1]$$

where  $N_D$  is the bulk carrier concentration.  $I_{D,SURFACE}$  is associated with  $R_{SURFACE}$  and accounts for the possibility that an accumulation layer is present at the channel surface, where “surface” is used to denote the channel interface opposite to that of the semiconductor/insulator interface. Figure 4.2 illustrates

FIG. 4.1. A schematic of the 3-layer model for a simplified bottom-gate TFT with an n-type channel.

an energy band diagram showing the formation of a surface accumulation layer at zero-bias for a bottom-gate TFT with an n-type channel. The semiconductor/insulator interface is idealized in Figure 4.2, neglecting any gate-semiconductor work function difference and interface state effects.

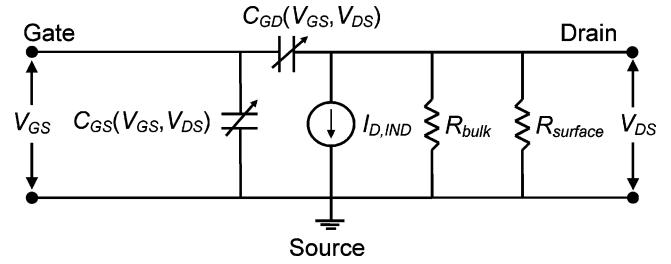

Mapping the model parameters into an equivalent circuit, in the same way as demonstrated in section III.A, yields,

$$I_D(V_{GS}, V_{DS}; Z, L, n_0, h, C_G, \mu, \mu_{SURFACE}, R_{SURFACE}; \text{none}), \quad [4.2]$$

where  $\mu$  and  $\mu_{SURFACE}$  represent the semiconductor/insulator interface and the surface mobilities respectively, and  $R_{SURFACE}$  represents the resistance of the surface accumulation layer. An equivalent circuit appropriate for the 3-layer model is given in

FIG. 4.2. Energy band diagram for an n-type TFT with a surface accumulation layer.

FIG. 4.3. An equivalent circuit for the 3-layer model.

Figure 4.3. Note that  $I_{D,IND}$  is a voltage-controlled current source that (implicitly) depends on  $V_{GS}$  and  $V_{DS}$ .

A summary of the variables, equations, regimes of operation, constraints, and model parameters constituting the 3-layer model is presented in Table 4.1. Only two additional parameters,  $\mu_{SURFACE}$  and  $R_{SURFACE}$ , are required to specify the 3-layer model in addition to those employed in the square-law model.

## B. Application of the 3-Layer Model Applied to $\text{SnO}_2$ Transparent Thin-Film Transistors

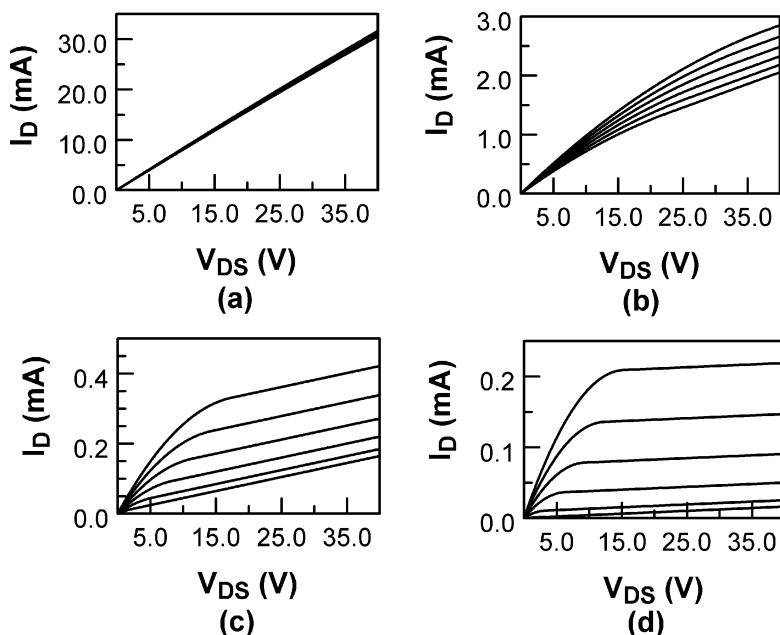

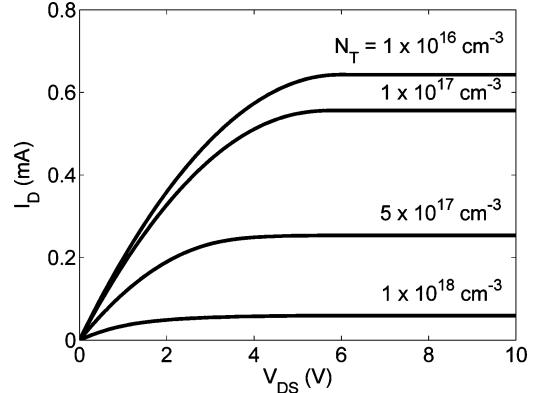

With the addition of  $R_{BULK}$  into the square-law model, a large initial carrier concentration can have a dramatic effect on  $I_D - V_{DS}$  curves, as shown in Figure 4.4. Figure 4.4(a)–(d) show the effect of different values of  $N_D$ , and therefore  $R_{BULK}$ , on the  $I_D - V_{DS}$  curves. The simulation shown in Figure 4.4(a), with a carrier concentration of  $10^{20} \text{ cm}^{-3}$ , essentially behaves as a simple linear resistor with a bulk resistance of  $2.5 \text{ k}\Omega$ . Consequently, nearly all of the current in this device flows through the bulk, resulting in linear  $I_D - V_{DS}$  curves with negligible gate voltage modulation. Figure 4.4(b) displays a very small amount of gate voltage modulation in the  $I_D - V_{DS}$  curves, whereas Figure 4.4(c) is beginning to behave similar to an ideal transistor. Thus, as  $N_D$  decreases, the percentage of the drain current that is attributed to gate-induced current ( $I_{D,IND}$ ) increases, resulting in more effective gate modulation in the  $I_D - V_{DS}$  curves. However, “hard” saturation of the  $I_D - V_{DS}$  curves is not obtained in any case, including Figure 4.4(d). The lack of “hard” saturation is in contradistinction to characteristics exhibited by real TFTs. This is a limitation of the 3-level model. By modeling the bulk and surface conduction paths as resistors, it is implicitly assumed that these conduction paths cannot be affected by the applied gate voltage. Moreover, it is implicitly assumed that the channel cannot be fully depleted. For real TFTs with  $V_{ON}$  as low as  $\sim 10 \text{ V}$ , drain current saturation is observed provided that the drain voltage is sufficiently large to obtain pinch-off.

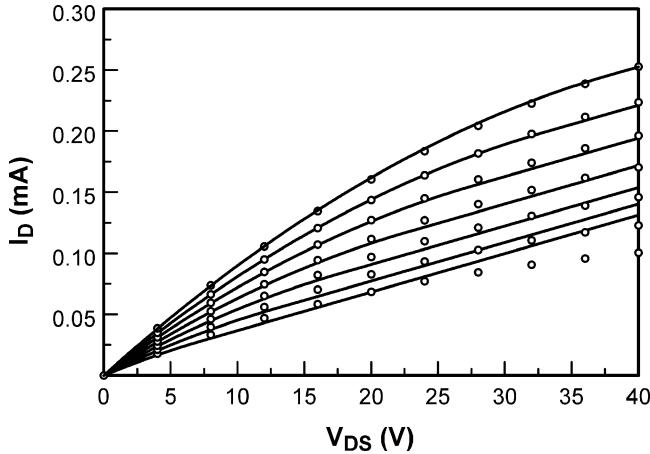

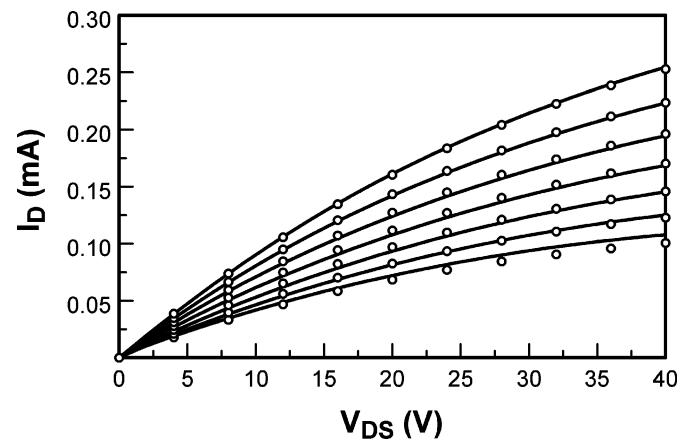

Figure 4.5 shows measured  $I_D - V_{DS}$  characteristics for a  $\text{SnO}_2$  TTFT with a simulated fit using the 3-layer model. The high initial carrier concentration results in non-saturating characteristics for the applied voltage range, as evident from Figure 4.5. Notice that the 3-layer model provides a reasonable fit to the measured data at high gate voltages. As  $V_{GS}$  is decreased and approaches  $V_{ON}$  (which is calculated to be  $\sim 17 \text{ V}$ ), the

TABLE 4.1

Summary of the 3-layer model

| Variable designation | Equation                                                                                                                                                                           |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Turn-on voltage      | $V_{ON} = \frac{-qhN_D}{C_G}$                                                                                                                                                      |

| Pinch-off condition  | $V_{DSAT} = V_{GS} - V_{ON}$                                                                                                                                                       |

| Bulk Resistance      | $R_{BULK} = \frac{L}{q\mu N_D h Z}$                                                                                                                                                |

| Regime of operation  | Equation                                                                                                                                                                           |

| Cut-off              | $I_D = \frac{V_{DS}}{R_{BULK}} + \frac{V_{DS}}{R_{SURFACE}}$                                                                                                                       |

| Pre-pinchoff         | $I_D = \frac{Z\mu C_G}{L} [(V_{GS} - V_{ON})V_{DS} - \frac{V_{DS}^2}{2}] + \frac{V_{DS}}{R_{BULK}} + \frac{V_{DS}}{R_{SURFACE}}$                                                   |

| Post-pinchoff        | $I_D = \frac{Z\mu C_G}{L} (V_{GS} - V_{ON})^2 + \frac{V_{DS}}{R_{BULK}} + \frac{V_{DS}}{R_{SURFACE}}$                                                                              |

| Model parameters     | Geometrical-based<br>Channel-based<br>Surface-based                                                                                                                                |

|                      | $V_{GS} < V_{ON}$<br>$V_{GS} \geq V_{ON}$<br>$V_{DS} \leq V_{DSAT}$<br>$V_{GS} \geq V_{ON}$<br>$V_{DS} > V_{DSAT}$<br>$Z, L, h, C_G$<br>$n_0, \mu$<br>$\mu_{SURFACE}, R_{SURFACE}$ |

3-layer model fit deteriorates. This deterioration is due to the fact that the 3-layer model assumes that the channel cannot be fully depleted. Therefore, the 3-layer model should be limited to qualitative (rather than quantitative) modeling to elucidate basic device operation. To alleviate the deficiencies of the 3-layer model, depletion near the drain must be accounted for, as accomplished in the comprehensive depletion-mode model, which is introduced in the next sub-section.

### C. Comprehensive Depletion-Mode Model

The comprehensive depletion-mode model presented in this sub-section addresses the deficiencies of the 3-layer model. A full derivation<sup>22–24</sup> of the comprehensive depletion-mode model is presented in section X.B.

Consider the nature of operation of an n-channel, depletion-mode TFT. When a positive gate voltage is applied, an accumulation layer forms at the insulator/semiconductor interface. When

FIG. 4.4. Simulated  $I_D - V_{DS}$  curves for varying values of the channel carrier concentration  $n_0$ . Plots (a)–(d) represent varying carrier concentrations of  $10^{20}, 10^{19}, 10^{18}, 10^{17} \text{ cm}^{-3}$  and result in  $V_{ON} \sim -230, -23, -2.3, -0.2 \text{ V}$ , respectively. Model parameters used in this simulation:  $Z/L = 5$ ,  $h = 100 \text{ nm}$ ,  $C_G = 7 \times 10^{-7} \text{ F/cm}^2$ ,  $\mu = 0.5 \text{ cm}^2/\text{V}\cdot\text{s}$ ,  $R_{SURFACE} = 10^9 \Omega$ .

FIG. 4.5. Measured  $I_D - V_{DS}$  curves (open circles) for a  $\text{SnO}_2$  TFT with a fit to the data (continuous lines) using the 3-layer model.  $V_{GS}$  is decreased from 20 V (top curve, showing maximum current) to  $-10$  V in 5 V increments. Model parameters used in this simulation:  $N_D = 1.3 \times 10^{18} \text{ cm}^{-3}$ ,  $Z/L = 5$ ,  $h = 60 \text{ nm}$ ,  $C_G = 7 \times 10^{-8} \text{ F/cm}^2$ ,  $\mu = 0.5 \text{ cm}^2/\text{V-s}$ , and  $R_{\text{SURFACE}} = 10^9 \Omega$ .

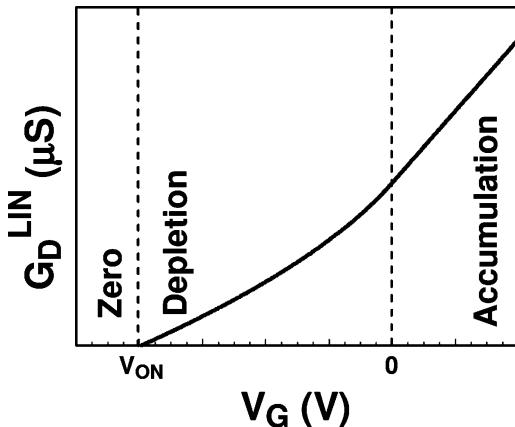

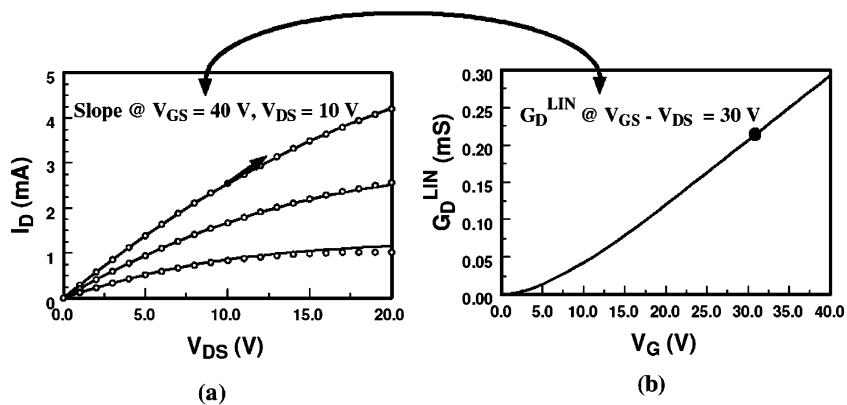

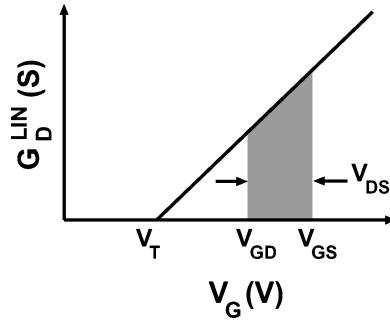

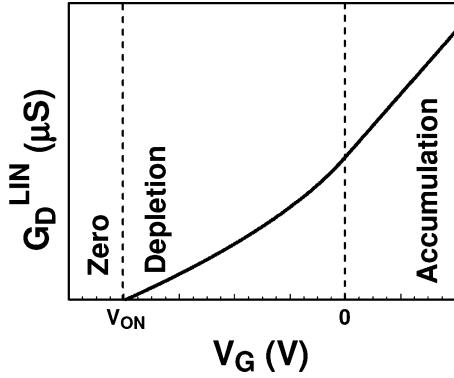

a negative bias is applied to the gate, the interface is in depletion, but it is still possible for current to flow. When  $V_G < V_{ON}$ , no current flows. The regions of operation just described are summarized in the channel conductance-gate voltage ( $G_D^{\text{LIN}} - V_G$ ) characteristic shown in Figure 4.6, where  $G_D^{\text{LIN}}$  designates that the channel conductance is evaluated in the linear region ( $V_{DS} \rightarrow 0$  V).

Two transitions are evident from the dashed lines in Figure 4.6. The first transition, from the zero region to the depletion region, is established by the turn-on voltage,  $V_{ON}$ ,

$$V_G \left( G_D^{\text{LIN}}|_{\text{DEPL}} = 0 \right) \equiv V_{ON} = V_P - \frac{qN_D h}{C_G}. \quad [4.3]$$

FIG. 4.6.  $G_D^{\text{LIN}} - V_G$  plot for an idealized depletion-mode TFT.

Notice that the first term on the right side of Eq. 4.3 represents the pinch-off voltage,  $V_P$ , which is the voltage dropped across the semiconductor when the channel is fully depleted.  $V_P$  is given by

$$V_P = -\frac{qN_D h^2}{2\epsilon_S}, \quad [4.4]$$

where  $\epsilon_S$  is the semiconductor permittivity. The second term in Eq. 4.3 is the voltage dropped across the insulator when the channel is fully depleted. Because  $V_P$  is a negative quantity,  $V_{ON}$  is thus, always a negative quantity, which is consistent with a depletion-mode TFT. The second transition, from depletion to accumulation, occurs at 0 V, assuming no semiconductor-metal work function difference or flat-band voltage shift.

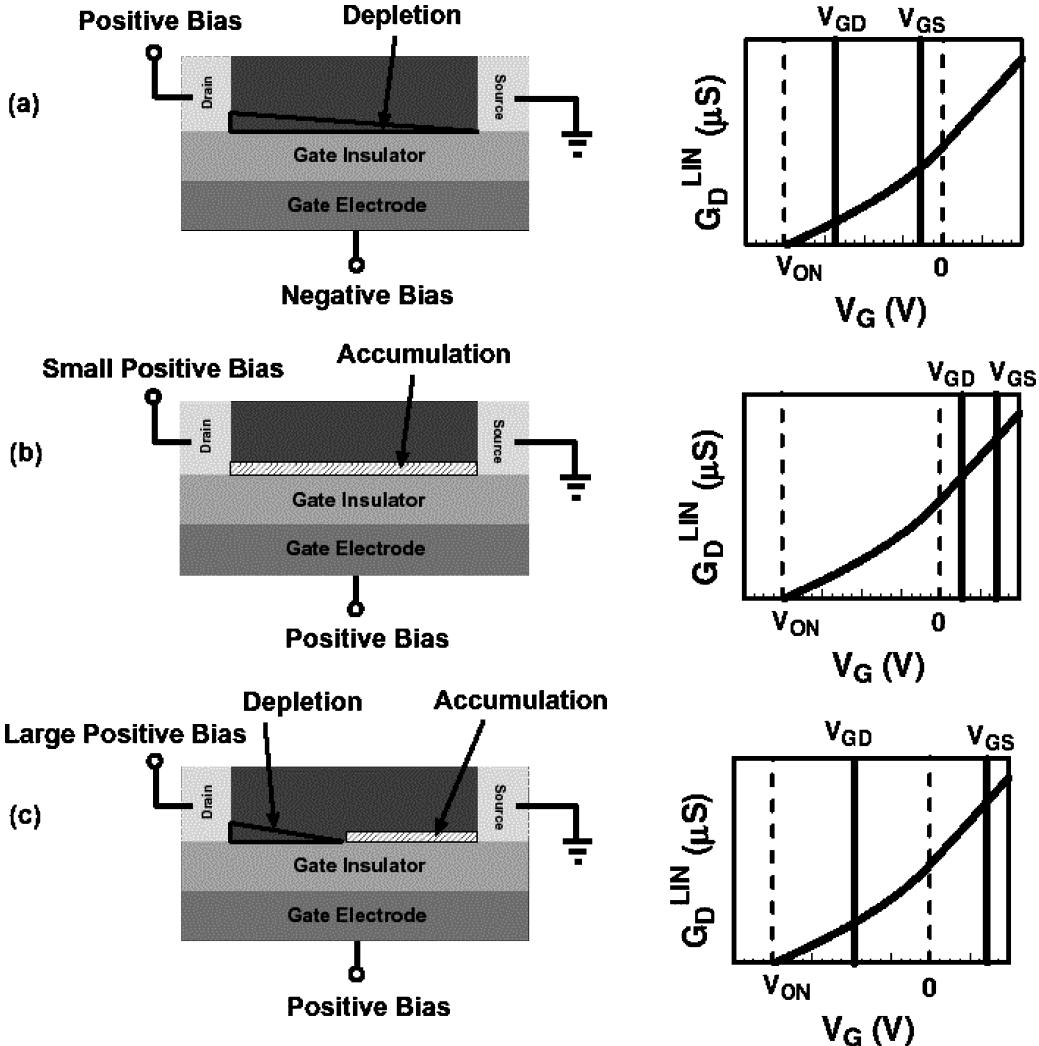

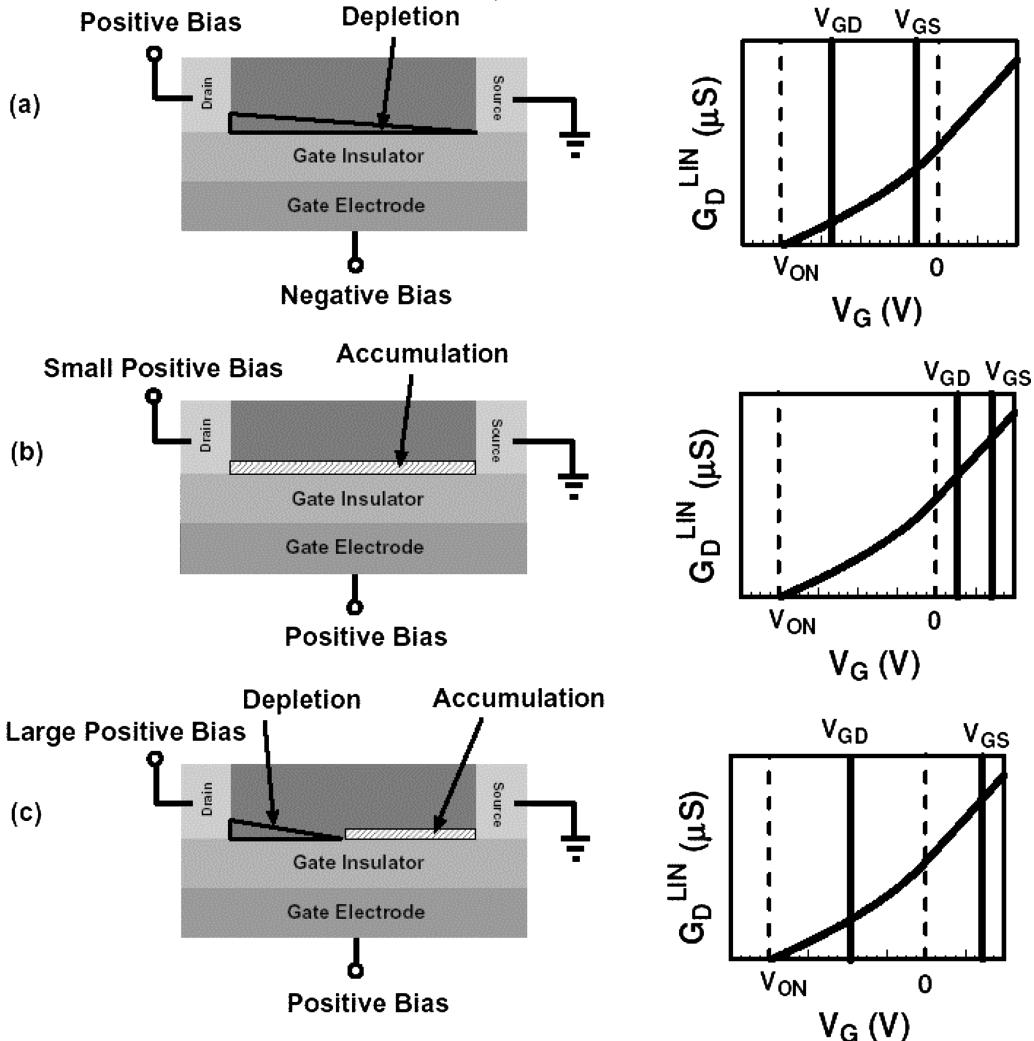

Now, consider several biasing schemes, indicated by the solid lines in the  $G_D^{\text{LIN}} - V_G$  plots shown in Figure 4.7. Note that the dashed lines separate the regions of operation (i.e., zero, depletion, and accumulation). Additionally, the corresponding TFT cross-sections are given to illustrate the nature of conduction. Figure 4.7(a) shows the device with applied voltages ( $V_{ON} < V_{GS} < 0$  V and  $V_{ON} < V_{GD} < 0$  V) such that a depletion region exists in the channel from the source to drain. Figure 4.7(b) shows the device with applied voltages ( $V_{GS} > 0$  V and  $V_{GD} > 0$  V) such that an accumulation region exists in the channel from the source to the drain. Figure 4.7(c) shows the intermediate case ( $V_{GS} > 0$  V and  $V_{ON} < V_{GD} \leq 0$  V) in which the channel is partially depleted and partially accumulated.

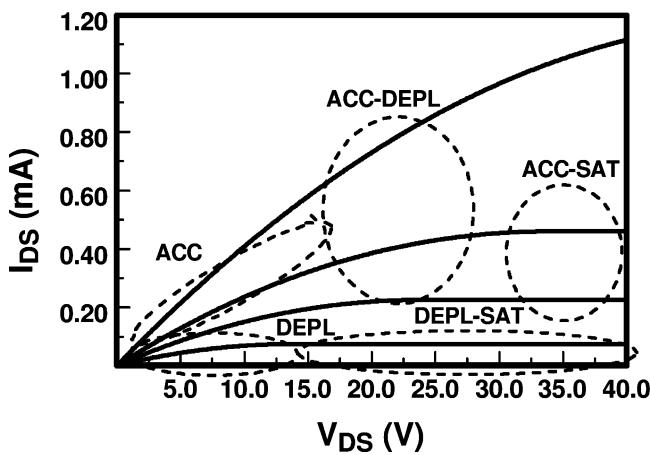

First, consider the depleted channel case indicated in Figure 4.7(a). A depletion region exists in the channel from the source to the drain, when both  $V_{GD}$  and  $V_{GS}$  are between  $V_{ON}$  and zero volts. Next, consider the accumulated-channel case shown in Figure 4.7(b). The channel near the source is accumulated when  $V_{GS} > 0$  V and the channel near the drain is accumulated when  $V_{GD} > 0$  V. In this case, the depletion-mode model accounts for the appreciable bulk carrier concentration by the addition of a resistor in parallel with  $I_{D,IND}$ . If the drain voltage is increased, such that  $V_{GD}$  decreases below 0 V, the channel near the drain is partially depleted, resulting in the situation shown in Figure 4.7(c). Because both an accumulation region and a depletion region exist along the length of the channel, both regions must be accounted for when calculating the channel conductance. Thus, the cases illustrated in Figure 4.7(a)–(c) correspond to the depletion (DEPL), accumulation (ACC), and accumulation-depletion (ACC-DEPL) regimes of TFT operation, respectively. The  $I_D - V_{DS}$  characteristics for these regimes, as well as, the depletion-saturation (DEPL-SAT) and accumulation-saturation (ACC-SAT) regimes are shown and identified in Figure 4.8.

Table 4.2(a) and (b) summarize the variables, definitions, and central equations constituting the comprehensive depletion-mode model. Additionally, the governing  $V_{DS}$  and  $V_{GS}$  constraint relationships for each operating regime and the model parameters are given in Table 4.2(b).

FIG. 4.7. Depletion-mode TFT cross-section and corresponding  $G_D^{LIN}$  –  $V_G$  plot showing three operating conditions: (a) the channel has a depletion region extending from the source to the drain, (b) the channel has an accumulation region extending from the source to the drain, and (c) the channel is depleted near the drain and is accumulated near the source. The dashed lines separate the regions of operation (i.e., zero, depletion, and accumulation). Thus, the magnitude of  $V_{GD}$  and  $V_{GS}$  (indicated by the solid lines) with respect to  $V_{ON}$  and zero volts determine which operating region applies.

TABLE 4.2(a)

Variable definition for the comprehensive n-channel, depletion-mode TFT model

| Variable designation          | Equation                                                                                                                                                                      |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pinch-off voltage             | $V_P = -\frac{qN_D h^2}{2\epsilon_S}$                                                                                                                                         |

| Turn-on voltage               | $V_{ON} = V_P - \frac{qN_D h}{C_G}$                                                                                                                                           |

| Saturation voltage            | $V_{DSAT} = V_{GS} - V_{ON}$                                                                                                                                                  |

| Channel conductance           | $\sigma = \mu q N_D$                                                                                                                                                          |

| Channel capacitance           | $C_S = \frac{\epsilon_S}{h}$                                                                                                                                                  |

| ACC-DEPL accumulation current | $I_{ACC} = \frac{Z\mu C_G}{2L} V_{GS}^2 + \frac{Zh\sigma}{L} V_{GS}$                                                                                                          |

| ACC-DEPL depletion current    | $I_{DEPL} = \frac{Z}{L} \sigma h [(1 + \frac{C_S}{C_G})(V_{DS} - V_{GS}) - \frac{2}{3} V_P (\frac{C_S^3}{C_G^3} - (\frac{C_S^2}{C_G^2} + \frac{V_{GD}}{V_P})^{\frac{3}{2}})]$ |

| ACC-DEPL saturation current   | $I_{DEPL2} = \frac{Z}{L} \sigma h [(1 + \frac{C_S}{C_G})(V_{ON}) - \frac{2}{3} V_P (\frac{C_S^3}{C_G^3} - (\frac{C_S^2}{C_G^2} + \frac{V_{ON}}{V_P})^{\frac{3}{2}})]$         |

TABLE 4.2(b)

Central equations and model parameters for the comprehensive n-channel, depletion-mode TFT model

| Regime of operation | Equation                                                                                                                                                                                              | Constraints                                        |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| DEPL                | $I_D = \frac{Z}{L} \sigma h [(1 + \frac{C_S}{C_G}) V_{DS} - \frac{2}{3} V_P ((\frac{C_S^2}{C_G^2} + \frac{V_{GS}}{V_P})^{\frac{3}{2}} - (\frac{C_S^2}{C_G^2} + \frac{V_{GD}}{V_P})^{\frac{3}{2}})]$   | $V_{ON} < V_{GS} < 0$<br>$V_{DS} < V_{DSAT}$       |

| DEPL-SAT            | $I_D = \frac{Z}{L} \sigma h [(1 + \frac{C_S}{C_G}) V_{DSAT} - \frac{2}{3} V_P ((\frac{C_S^2}{C_G^2} + \frac{V_{GS}}{V_P})^{\frac{3}{2}} - (\frac{C_S^2}{C_G^2} + \frac{V_{ON}}{V_P})^{\frac{3}{2}})]$ | $V_{ON} < V_{GS} < 0$<br>$V_{DS} \geq V_{DSAT}$    |

| ACC                 | $I_D = \frac{Z}{L} [\mu C_G (V_{GS} V_{DS} - \frac{V_{DS}^2}{2}) + \sigma h V_{DS}]$                                                                                                                  | $V_{GS} \geq 0$<br>$V_{DS} < V_{GS}$               |

| ACC-DEPL            | $I_D = I_{ACC} + I_{DEPL}$                                                                                                                                                                            | $V_{GS} \geq 0$<br>$V_{DSAT} > V_{DS} \geq V_{GS}$ |

| ACC-SAT             | $I_D = I_{ACC} + I_{DEPL2}$                                                                                                                                                                           | $V_{GS} \geq 0$<br>$V_{DS} \geq V_{DSAT}$          |

| Model parameters    | Geometrical-based<br>Channel-based                                                                                                                                                                    | $Z, L, h, C_G$<br>$N_D, \mu, \varepsilon_S$        |

Figure 4.9 shows measured  $I_D - V_{DS}$  characteristics for a  $\text{SnO}_2$  TTFT with a simulated fit using the comprehensive depletion-mode model. Notice that the comprehensive depletion mode model is able to simulate a wider range of applied gate bias than the 3-layer model fit to the same data shown in Figure 4.5. The small deviation between the bottom simulated curve of Figure 4.9 and the measured data is attributed to the invalid constant mobility assumption employed for this simulation. Measured mobility trends verify this assertion.

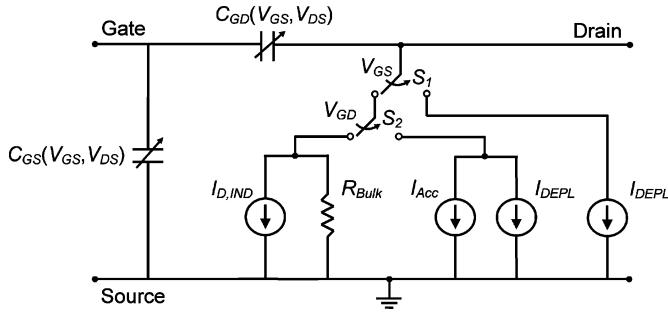

An equivalent circuit corresponding to the comprehensive n-channel, depletion-mode model is given in Figure 4.10. Two switches ( $S_1$  and  $S_2$ ) are used to select which of the three pos-

sible channel current paths is operative. Switch  $S_1$  is controlled by  $V_{GS}$ , and establishes whether the channel near the source is in accumulation ( $V_{GS} > 0$  V) or depletion ( $V_{GS} < 0$  V). Switch  $S_2$  depends on  $V_{GD}$ , and determines whether the channel near the drain is in accumulation ( $V_{GD} > 0$  V) or depletion ( $V_{GD} < 0$  V). The current path on the left corresponds to the ACC regime ( $V_{GS} > 0$  V and  $V_{GD} > 0$  V), which includes a bulk resistance in parallel with the gate-induced current; this operating regime is equivalent to the 3-layer model (if surface conduction is neglected). The middle path corresponds to the ACC-DEPL regime ( $V_{GS} > 0$  V and  $V_{GD} < 0$  V). Finally, the path to the right corresponds to the DEPL regime ( $V_{GS} < 0$  V and  $V_{GD} < 0$  V).

It can be shown that the comprehensive n-channel, depletion-mode TFT model simplifies to the square-law model in the limit

FIG. 4.8.  $I_D - V_{DS}$  characteristic simulated using the comprehensive depletion-mode TFT model of Table 3.1 using the model parameters listed in Table 3.2. The five regimes of device operation are indicated.  $V_{GS}$  is decreased from 30 V (top curve, showing maximum current) to  $-10$  V in 10 V steps. Model parameters used in this simulation:  $Z/L = 10$ ,  $h = 80$  nm,  $C_G = 1.7 \times 10^{-9}$  F/cm $^2$ ,  $\mu = 5$  cm $^2$ /V-s, and  $N_D = 3 \times 10^{17}$  cm $^{-3}$ .

FIG. 4.9. Measured  $I_D - V_{DS}$  curves (open circles) for a  $\text{SnO}_2$  TTFT with a fit to the data (continuous lines) using the depletion-mode model.  $V_{GS}$  is decreased from 20 V (top curve, showing maximum current) to  $-10$  V in 5 V increments. Model parameters used in this simulation:  $N_D = 2.2 \times 10^{18}$  cm $^{-3}$ ,  $Z/L = 5$ ,  $h = 60$  nm,  $C_G = 7 \times 10^{-8}$  F/cm $^2$ , and  $\mu = 0.3$  cm $^2$ /V-s.

FIG. 4.10. An equivalent circuit for the comprehensive n-channel, depletion-mode model. The switches  $S_1$  and  $S_2$  establish which of the three channel current paths is operative, based on the magnitude and polarity of  $V_{GS}$  and  $V_{GD}$ .

$C_S \gg C_G$ . There are several ways to justify the limit  $C_S \gg C_G$ . Perhaps the simplest justification involves recognizing that if this limit is satisfied, all of the voltage applied to the gate of the TFT is dropped across the insulator. This implies that the charge induced in the channel is equal to  $C_G(V_{GS} - V_{ON})$  so that

$$G_D^{LIN} = \frac{Z}{L} C_G (V_{GS} - V_{ON}), \quad [4.5]$$

which is identical to Eq. 10.16, which is used to derive the square-law model, except that  $V_T$  is replaced by  $V_{ON}$ .

## V. DISCRETE TRAP MODEL

The objective of this section is to present an overview of the discrete trap model and to elucidate the primary device physics consequences of carrier trapping. The initial portion of this derivation was previously introduced by Sze.<sup>3</sup>

### A. Model Overview

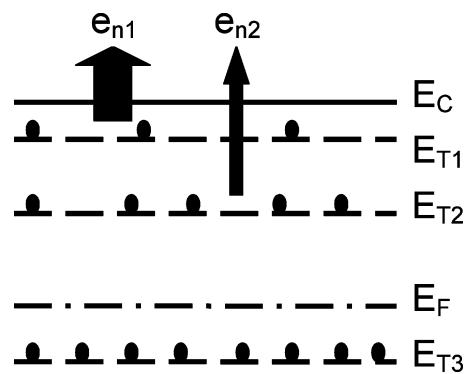

Although it is more likely that there is a distribution of traps over a specific energy range, a discrete trap is used here to simplify mathematical analysis and to provide insight with regard to the effect of traps on TFT performance. The discrete trap under consideration in this model is assumed to interact only with conduction band electrons, not valence band holes. Therefore, it is characterized by its ionization energy,  $E_T$ , capture cross-section,  $\sigma_n$ , and density,  $N_T$ .

Assuming that the average conduction band electron velocity and capture cross-section is constant, the rate of conduction band trapping is a function of the empty trap density and the density of electrons present in the conduction band. In contrast, the rate of emission from the trap state to the conduction band is a function of the filled trap density and the conduction band electron density when the Fermi-level,  $E_F$ , is equal  $E_T$ . Mathematically, the rate of conduction band trapping is expressed as,  $\bar{v}\sigma_n(N_T - n_t)n_c$ , where  $\bar{v}$  is the average conduction band electron velocity,  $(N_T - n_t)$  is the density of empty traps, and  $n_c$  is the density of electrons present in the conduction band. The

rate of electron emission from the trap state to the conduction band is expressed as,  $\bar{v}\sigma_n n_t n_1$ , where  $n_1$  is the conduction band electron density when  $E_F = E_T$  and is given by

$$n_1 = N_c e^{\left(\frac{-E_T}{k_B T}\right)}, \quad [5.1]$$

where  $N_c$  is the effective density of states of the conduction band and  $k_B$  is Boltzmann's constant.

When considering the  $Q = C \times V$  relationship for the discrete trap model, it is important to recognize that the total charge induced in the channel by the application of a gate voltage is distributed into both conduction band and trap states,

$$\begin{aligned} q(\Delta n_c + \Delta n_t) &= q[(n_c + n_t) - (n_{co} + n_{to})] \\ &= \frac{C_G}{h} [V_{GS} - V(y)], \end{aligned} \quad [5.2]$$

where  $n_{co}$  and  $n_{to}$  are initial, zero-bias densities of free conduction band electrons and trapped electrons, respectively. Rearrangement of Eq. 5.2 leads to

$$q(n_c + n_t) = \frac{C_G}{h} [V_{GS} - V(y) - V_{ON}], \quad [5.3]$$

where  $V_{ON}$ , the turn-on voltage, is given by

$$V_{ON} = -\frac{q h}{C_G} (n_{co} + n_{to}). \quad [5.4]$$

Using Eq. 5.2 in conjunction with the steady-state assumption (i.e., the conduction band trapping rate is equivalent to the trap emission rate), the voltage along the channel can be solved for and integrated to determine the drain current, as shown in section X.C.

Table 5.1 summarizes the TFT discrete trap model. Note that the  $V_{DS}$  and  $V_{GS}$  constraint equations, the  $V_{DSAT}$  pinch-off equation, and the geometrical and channel-related model parameters are all identical to those employed in the square-law model. In

TABLE 5.1

A summary of the discrete trap model

| Variable designation         | Equation                                                                                                           |

|------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Turn-on voltage              | $V_{ON} = -\frac{q h}{C_G} (n_{co} + n_{to})$                                                                      |

| Pinch-off condition          | $V_{DSAT} = V_{GS} - V_{ON}$                                                                                       |

| Regime of operation Equation | Constraints                                                                                                        |

| Cut-off                      | $I_D = 0 \quad V_{GS} < V_{ON}$                                                                                    |

| Pre-pinch-off                | $V_{GS} \geq V_{ON} \quad V_{DS} \leq V_{DSAT}$                                                                    |

| Post-pinch-off               | $V_{GS} \geq V_{ON} \quad V_{DS} > V_{DSAT}$                                                                       |

| Model parameters             | Geometrical-based $Z, L, h, C_G$<br>Channel-based $\mu, n_{co}$<br>Trap-related $N_T, E_T, n_{to}$<br>Physical $T$ |

contrast, the pre-pinch-off and the post-pinch-off model equations, which are derived in section X.C, are more complex due to the inclusion of discrete trap effects.

## B. Simulation Results: Subthreshold Current Considerations

The previously discussed models have not explicitly considered the threshold voltage,  $V_T$ , or subthreshold current, that is, the drain current obtained when the gate voltage is less than  $V_T$ . Before considering subthreshold current,  $V_T$  must be clearly considered and established. Here,  $V_T$  is a demarcation point, establishing the onset of subthreshold current. Additionally,  $V_T$  is sometimes used to quantify the onset of drain current conduction.

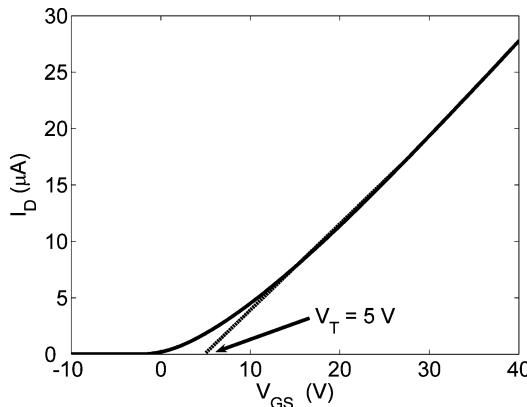

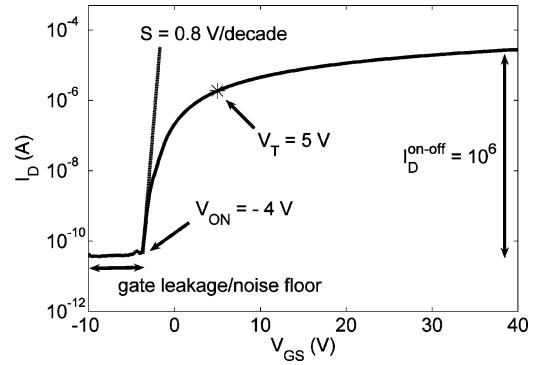

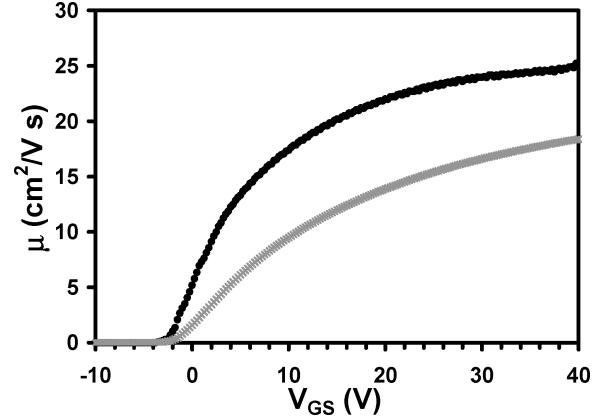

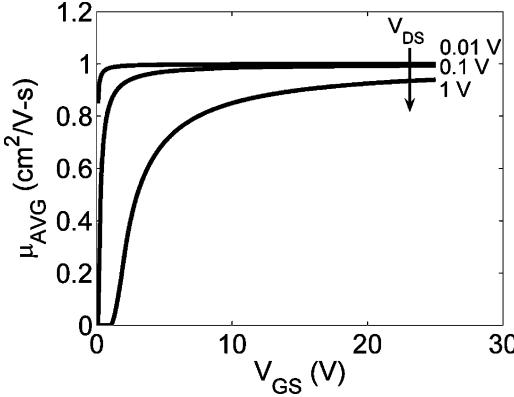

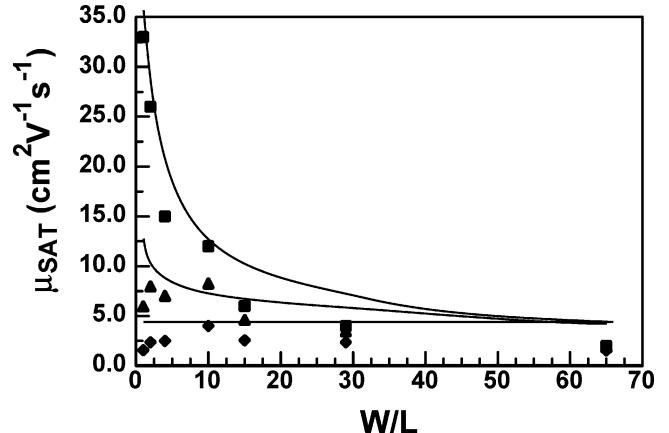

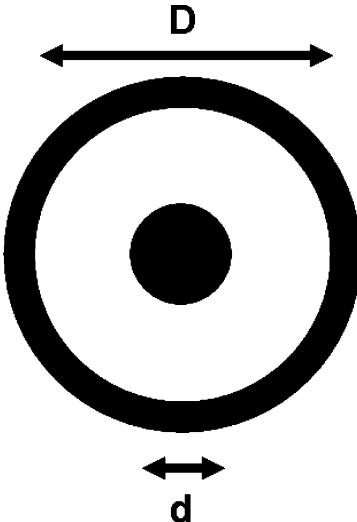

When considering  $V_T$  and  $V_{ON}$ , their relative effectiveness as drain current onset parameters is an issue. Figure 5.1 illustrates the estimation of  $V_T$  via simple linear extrapolation of an  $I_D - V_{GS}$  transfer curve for a prototypical zinc tin oxide TFT. As shown, the extrapolated value of  $V_T$  is  $\sim 5$  V. Now, consider  $V_{ON}$ , which is evaluated using a  $\log(I_D) - V_{GS}$  transfer, as shown in Figure 5.2, and results in a value of  $-4$  V for the same device.  $V_{ON}$  corresponds to the initial onset of appreciable drain current measured on a  $\log(I_D) - V_{GS}$  transfer curve. This drain current onset occurs when  $I_D$  is larger than the gate leakage and/or the noise floor, which is established by the device under test and the precision of the measurement instrumentation. It is apparent from Figure 5.2 that  $V_{ON}$  is a more precise parameter to quantify drain current onset than  $V_T^{25}$ . Thus, the authors propose the use of  $V_{ON}$  as the preferred drain onset device electrical parameter.

The other parameters labeled in Figure 5.2 are the  $S$  parameter and the drain current on-to-off ratio.  $S$  is typically referred to as the subthreshold swing, which is given by  $S = \frac{\partial V_{GS}}{\partial \log(I_D)}|_{\min}$ , and characterizes the effectiveness of the gate voltage in reducing the drain current to zero. A small value of  $S$  is desirable

FIG. 5.1. Drain current-gate voltage ( $I_D - V_{GS}$ ) transfer curve for a zinc tin oxide, n-channel TFT. The threshold voltage is estimated to be  $\sim 5$  V via extrapolation of the linear portion of this curve. Geometrical parameters for this TFT are  $Z/L = 5:1$  and  $C_G = 3.45 \times 10^{-8}$  F/cm $^2$ .

FIG. 5.2.  $\log(I_D) - V_{GS}$  transfer curve for a zinc tin oxide, n-channel TFT. The voltage at which the TFT turns on is  $-4$  V. The previously extracted value of the threshold voltage,  $V_T = 5$  V does not correspond to any obvious drain current onset. Geometrical parameters for this TFT are  $Z/L = 5:1$  and  $C_G = 3.45 \times 10^{-8}$  F/cm $^2$ .

because this corresponds to a very sharp transition from on to off. The drain current on-to-off ratio,  $I_D^{on-off}$ , is established by the maximum drain current and the gate leakage/noise floor. A large  $I_D^{on-off}$  is desirable, because this corresponds to a more effective switch.

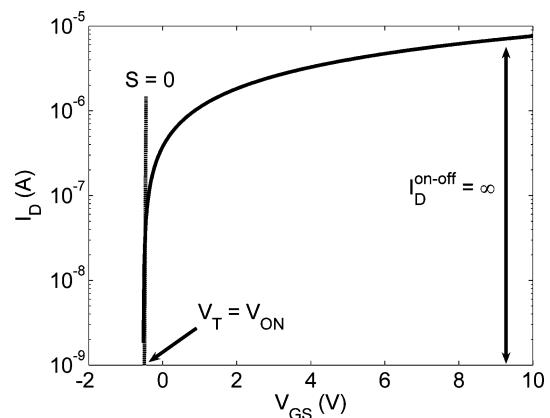

Now, consider the ideal  $\log(I_D) - V_{GS}$  transfer curve shown in Figure 5.3. Note that “ideal” refers to use of the ideal square-law model, neglecting the effect of traps and of diffusion current in establishing the subthreshold current.  $V_T = V_{ON}$ ,  $S = 0$ , and  $I_D^{on-off} = \infty$  are obtained for the ideal square-law model, as indicated in Figure 5.3. Ideal values for  $V_T$  and  $S$  are obtained because electron trapping in the channel and/or at channel interfaces is neglected. Moreover,  $S = 0$  for this ideal TFT, whereas  $S$  can only be as low as 60 mV/decade for a MOSFET, in which

FIG. 5.3.  $\log(I_D) - V_{GS}$  transfer curve simulation using the square-law model. In this ideal case,  $S = 0$  V/decade,  $V_T = V_{ON}$ , and the drain current on-to-off ratio is infinite. For this simulation  $V_{DS} = 100$  mV,  $Z/L = 6:1$ ,  $h = 20$  nm,  $C_G = 6.04 \times 10^{-8}$  F/cm $^2$ ,  $\mu = 100$  cm $^2$ /V-s, and  $n_o = 1 \times 10^{17}$  cm $^{-3}$ .

FIG. 5.4.  $I_D - V_{GS}$  and  $\log(I_D) - V_{GS}$  transfer curves simulated using the discrete trap model. For this simulation,  $T = 300$  K,  $V_{DS} = 1$  V,  $N_T = 5 \times 10^{17}$  cm $^{-3}$ ,  $E_T = 0.15$  eV below the conduction band minimum,  $Z/L = 6:1$ ,  $h = 20$  nm,  $C_G = 6.04 \times 10^{-8}$  F/cm $^2$ ,  $\mu = 100$  cm $^2$ /V-s, and  $n_{co} = 1 \times 10^{15}$  cm $^{-3}$ .

subthreshold current is modeled as diffusion current.<sup>26</sup>  $I_D^{on-off}$  is infinite because the ideal square-law model ignores gate leakage and instrumentation noise. Thus, assessment of  $S$  and  $I_D^{on-off}$  require “real world” considerations involving traps and gate leakage/measurement noise to be taken into account.

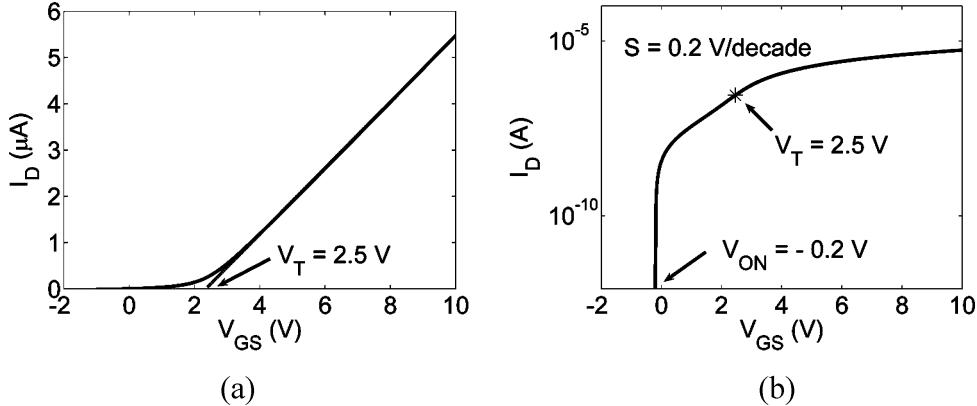

Figure 5.4 shows simulated  $I_D - V_{GS}$  and  $\log(I_D) - V_{GS}$  transfer curves for a TFT using the discrete trap model. From Figures 5.4(a) and 5.4(b),  $V_T$  is estimated via linear extrapolation as  $\sim 2.5$  V and  $V_{ON}$  is estimated to be approximately  $-0.2$  V, respectively.

Recall that the turn-on voltage is given by

$$V_{ON} = -\frac{qh}{C_G}(n_{co} + n_{to}), \quad [5.5]$$

where  $n_{co}$  and  $n_{to}$  correspond to the density of conduction band electrons and occupied trap states at zero bias. Because  $n_{co}$  is chosen to be low,  $V_{ON}$  is quite small for this simulation, that is,  $V_{ON}$  is  $\sim -0.2$  V. A negative value of  $V_{ON}$ , as seen in this case, requires that a negative gate voltage must be applied to remove free and trapped electrons from the channel.

$V_T$  can also be quantitatively defined within the context of the discrete trap model. Based on the discrete trap model,  $V_T$  is equivalent to the gate voltage required to fill all traps. This  $V_T$  is given by,

$$V_T = \frac{qh}{C_G}(N_T - n_{to}) + \frac{qh}{C_G}(n_1 - n_{co}) \quad [5.6a]$$

$$= V_{TRAP} + V_{ELECTRON}. \quad [5.6b]$$

$V_T$  is composed of two constituents,  $V_{TRAP}$  and  $V_{ELECTRON}$ .  $V_{TRAP}$  is associated to the gate voltage required to fill the empty traps,  $(N_T - n_{to})$ . However,  $V_{TRAP}$  neglects the change in conduction band electron density with applied gate voltage. This change is accounted for with  $V_{ELECTRON}$ . Moreover, evaluating Eq. 5.6a using simulation parameters yields  $V_T = 2.5$  V, which is equivalent to the estimate obtained from linear extrapolation of Figure 5.4(a).

Returning to Figure 5.4(b), as the gate voltage increases above  $V_{ON}$ , the drain current increases abruptly with an extremely large slope. As  $E_F$  moves closer to  $E_C$  and  $E_T$ , the steady-state trap occupancy increases, because  $E_T - E_F$  decreases. Thus, between  $V_{ON}$  and  $V_T$ , that is,  $-0.2 \leq V_{GS} \leq 2.5$  V, the slope of the  $\log(I_D) - V_{GS}$  curve is controlled by the rate of steady-state trapping and results in a non-zero value of  $S$ ; for the simulation shown in Figure 5.4(b),  $S$  is  $\sim 0.2$  V/decade. At gate voltages greater than  $V_T$ , the Fermi level moves above the trap level, so that  $E_T - E_F$  is negative and essentially all the traps are filled. Any further increase in the gate voltage results in further accumulation of free electrons in the conduction band, corresponding to TFT operation without the influence of traps.

Comparing the  $\log(I_D) - V_{GS}$  plots for a real TFT and a simulated TFT with a discrete trap, as shown in Figures 5.2 and 5.4(b), respectively, it is apparent that the simulated curve is dissimilar to the measured curve (i.e., the simulated curve has a kink in the current near  $V_T$ ). This discrepancy is likely due to the discrete trap assumption (which is employed for computational simplicity); it is likely that there is a distribution of traps over a specific energy range.

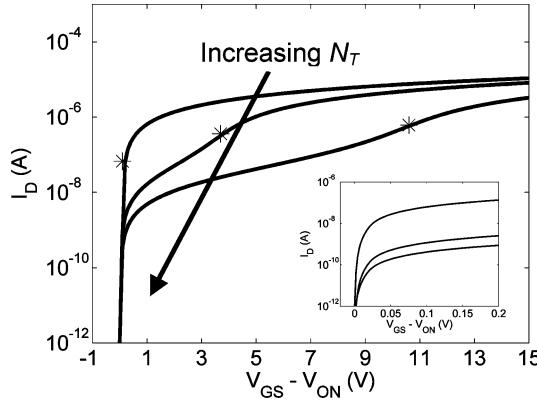

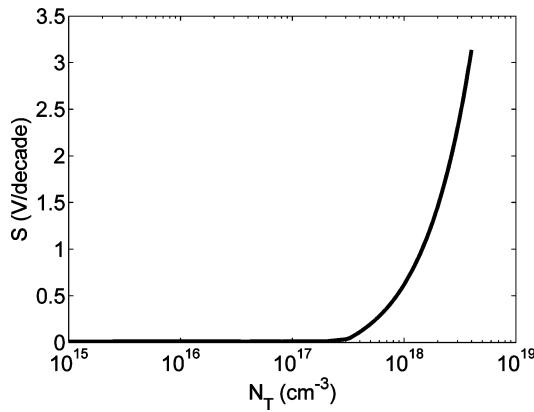

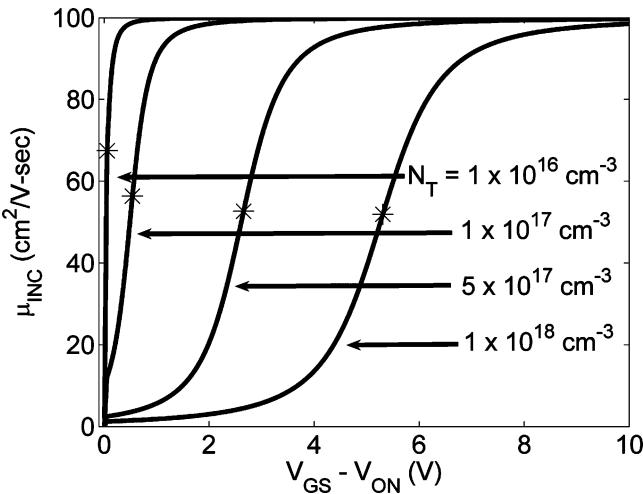

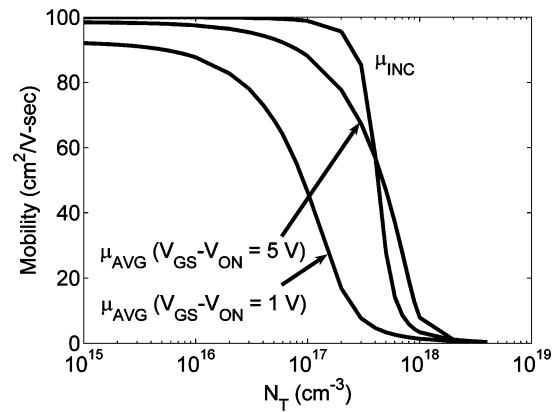

Simulated  $\log(I_D) - (V_{GS} - V_{ON})$  transfer characteristics for three trap densities with a constant trap depth (i.e.,  $E_T \sim -0.15$  eV) are shown in Figure 5.5. For a trap density of  $1 \times 10^{15}$  cm $^{-3}$ ,  $V_{TRAP}$  is negligible. Thus, the corresponding  $\log(I_D)$  curve is close to that of an ideal TFT with no traps. However, as  $N_T$  is increased, the drain current degrades. Correspondingly,  $V_{TRAP}$  and  $S$  increase with increasing trap density;  $V_{TRAP} - V_{ON} \sim 0.08$ , 3.8, and 10.7 V and  $S \sim 0.01$ , 0.3685, and 1.46 V/decade for  $N_T = 1 \times 10^{15}$ ,  $7 \times 10^{17}$ , and  $2 \times 10^{18}$  cm $^{-3}$ , respectively.  $S$  as a function of  $N_T$  is shown in Figure 5.6;  $S$  is initially very small for trap densities less than  $1 \times 10^{17}$  cm $^{-3}$ , but increases significantly thereafter.

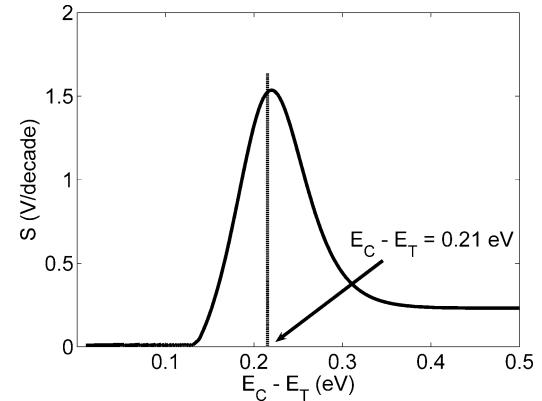

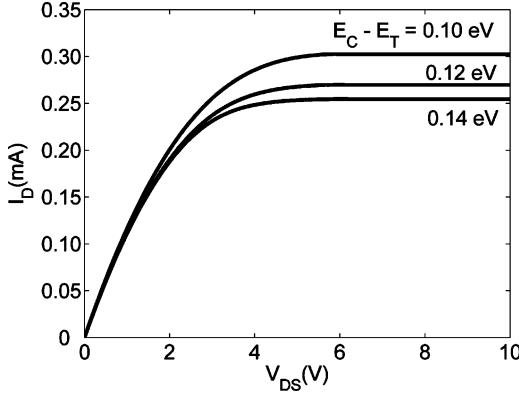

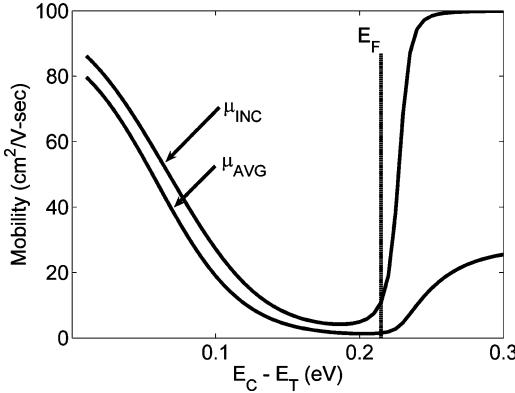

The dependence of  $E_T$  on  $S$  is shown in Figure 5.7 via simulation using the discrete trap model. For this simulation  $E_F = 0.21$  eV below the conduction band, as established by  $n_{co}$ . As

FIG. 5.5. Simulated  $\log(I_D) - (V_{GS} - V_{ON})$  transfer curves as a function of trap density,  $N_T$ , for a TFT using the discrete trap model. The arrow indicates the direction of increasing  $N_T$ . These curves correspond to  $N_T$  values of  $1 \times 10^{15}$ ,  $7 \times 10^{17}$ , and  $2 \times 10^{18} \text{ cm}^{-3}$  and  $V_{ON}$  values of  $-0.54$ ,  $-3.8$ ,  $-10$  V, respectively.  $V_{TRAP}$  is represented by “\*” on each  $\log(I_D)$  curve. (Inset) The transfer characteristic near  $V_{GS} - V_{ON} = 0$  V is shown in the inset. For these simulations,  $V_{DS} = 1$  V,  $Z/L = 6:1$ ,  $h = 20$  nm,  $C_G = 6.04 \times 10^{-8}$  F/cm $^2$ ,  $\mu = 100$  cm $^2$ /V-s, and  $n_{co} = 1 \times 10^{15} \text{ cm}^{-3}$ .

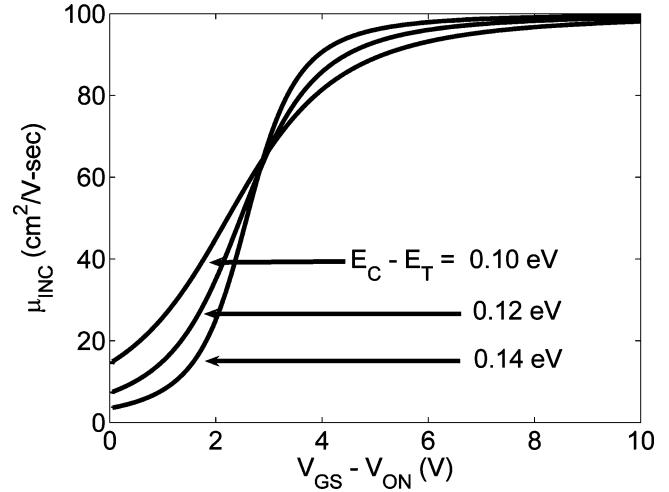

shown in Figure 5.7,  $S$  is small for shallow traps and increases near  $E_F$ , but then decreases then decreases beyond  $E_F$ . This relationship between  $S$  and  $E_T$  is attributed to the trap re-emission rate and occupancy, as discussed in the following.